CVA CHIP GALLERY

Last updated April 25, 2005

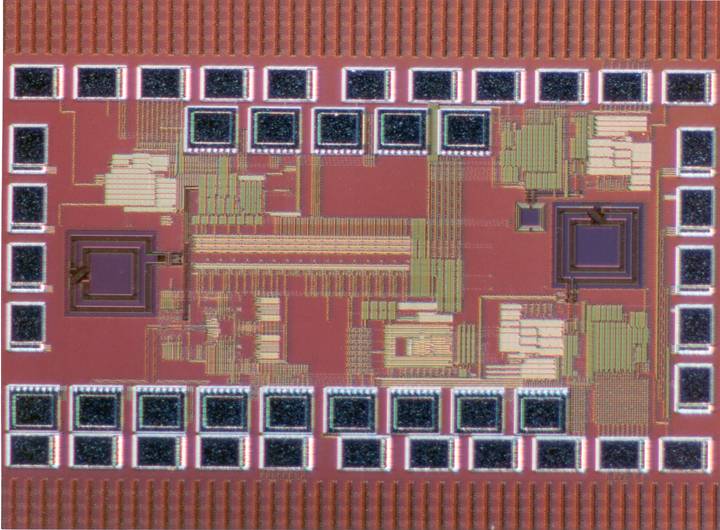

2003: 20Gb/s 0.13um CMOS Serial Link Transmitter

This 700um x 1.1mm die uses an integrated LC oscillator to directly modulate the output driver,

thereby achieving 20Gb/s serial output data, while burning 150mW.

Patrick Chiang, William J. Dally, Ming-Ju Edward Lee, Ramesh Senthinathan, Yangjin Oh, and Mark Horowitz.

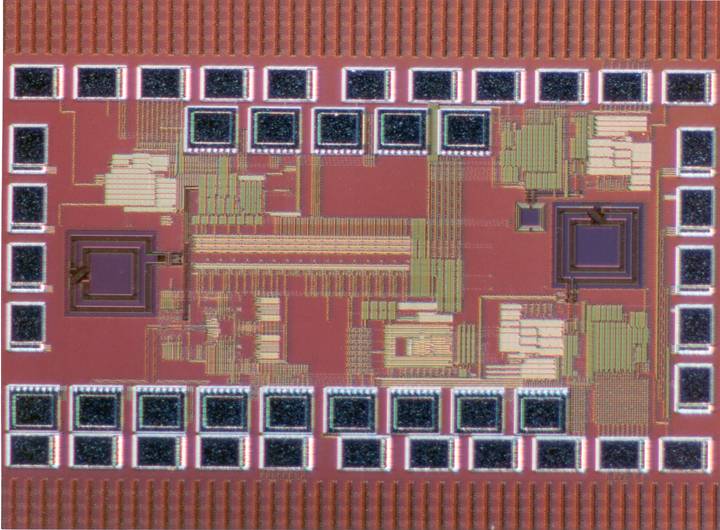

2002: Imagine Stream Processor

The prototype Imagine processor is a 21-million transistor chip, implemented

in a 0.15 micron CMOS process. At 232 MHz, a peak performance of 9.3 GFLOPS

is achieved while dissipating 6.4 Watts with a die size measuring 16 mm on a

side.

Brucek Khailany, Scott Rixner, Ujval J. Kapasi, Peter Mattson, Jinyung

Namkoong, John D. Owens, Brian Towles, Andrew Chang, and William J. Dally.

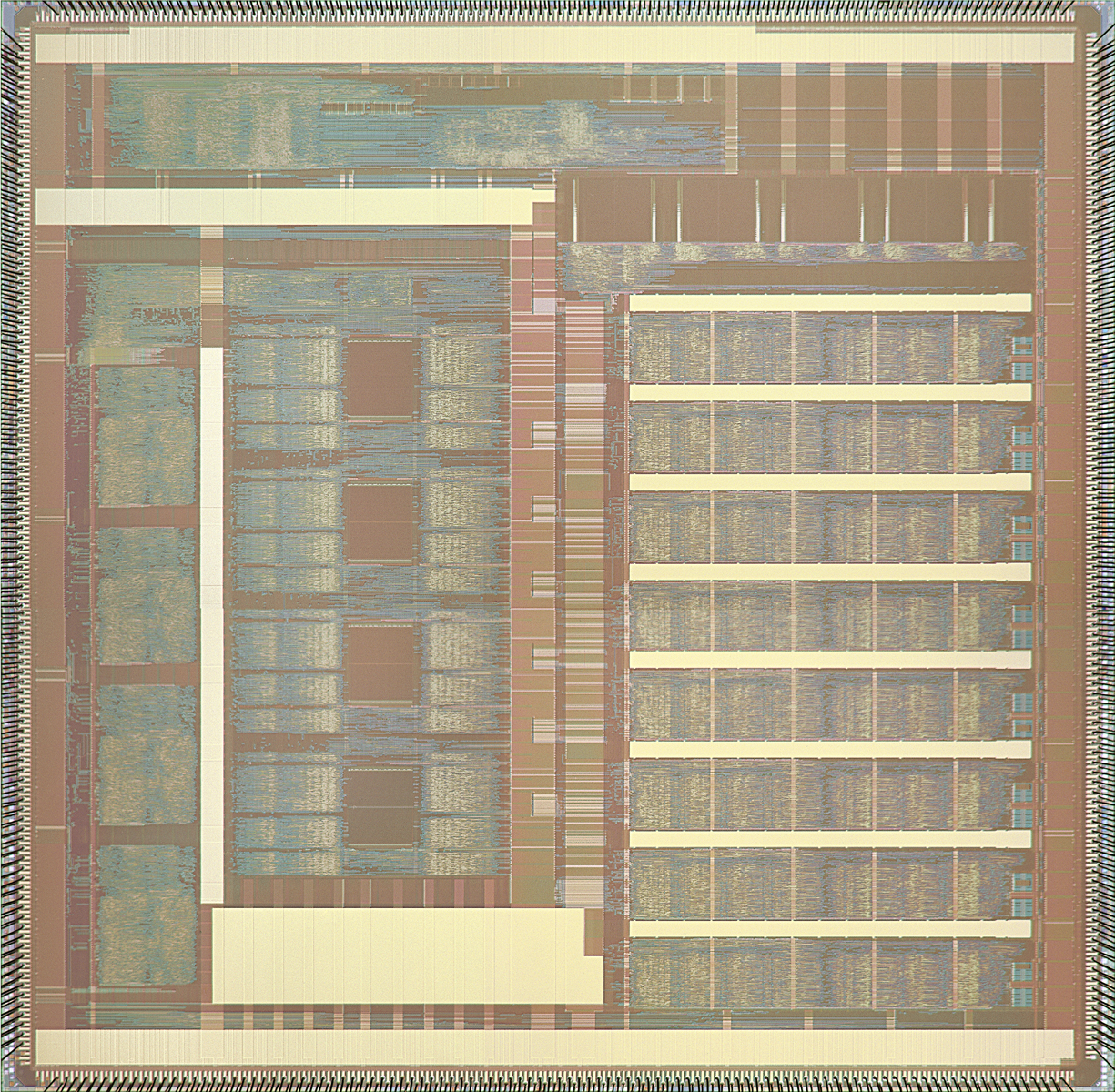

2001: Monolithic Chaotic Communications System This 1mm x 2mm

0.25um CMOS pulse position modulation(PPM) transceiver uses chaotic

modulation for pulse dithering, increasing security, decreasing power

spectral density, and decreased sychronization time.

Patrick Chiang, Ming-Ju Edward Lee, and William J. Dally.

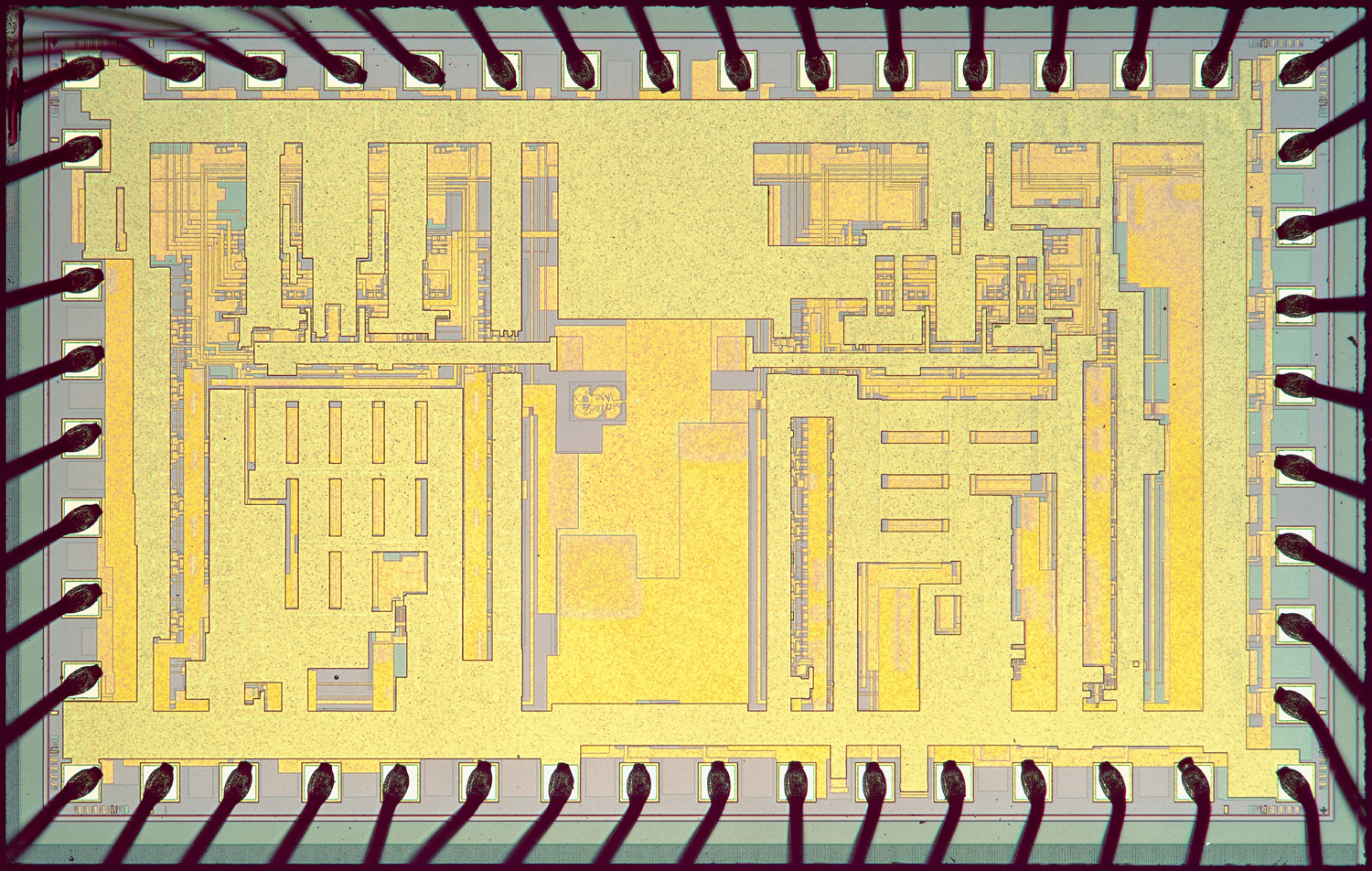

1999: 90mW 4Gb/s Equalized I/O Circuit . This 0.1 sq mm

CMOS serial link circuit is fabricated 2.5V 0.25um CMOS NWell process.

Ming-Ju Edward Lee, Patrick Chiang, and William J. Dally.

1998: Multi-ALU Processor (MAP). This 5-million transistor 18.25mm x 18.3mm chip is

fabricated in a 3.3V 0.5um Leff, 5-level metal CMOS technology and is the

core processing element of each node in the M-Machine multicomputer and

includes 7 execution units, 44KB on-chip cache, and hardware support for

multithreading.

Stephen Keckler, Andrew Chang, Whay Sing Lee, Nicholas Carter, and William J. Dally.

1997: Fast Links.

William J. Dally and John Poulton (UNC)

1995: Reliable Router. This 100MHz 13.5mm x 15mm network switch

element is fabricated in 5.0V 0.8um HP26 CMOS process. It is the core building block

for a 2-D Mesh network with a useful link bandwidth of 3.2 Gbit/sec. The

Reliable Router chip incorporates adaptive routing, link-level

re-transmission, and a unique token protocol to maximize reliability. It

implements queueless, low-latency pleisochronous channel interfaces and

simultaneous bidirectional signaling to maximize performance.

Larry Dennison, Thucydides Xanthopoulos, Kinhong Kan, Dan Hartman, Jeff Bowers, and William J. Dally.

1991 Message Driven Processor (MDP). This 1.1-million transistor 10.2mm x 15mm chip is

fabricated in a 5.0V 1um CMOS process and is the core processing element in each node of the 1024-node J-Machine. The MDP

is a tagged architecture and includes a 32bit ALU; integrated network interface

and 3D-Mesh Router; and 4KWords of software managed on-chip memory.

William J. Dally, Stuart Fiske, John Keen, Richard Lethin, Peter

Nuth, Waldemar Horwat, Michael Noakes, Scott Furman

1983: Quarternary Serial Multiplier.

William J. Dally.

1980: Stamp Processor.

William J. Dally.

achang@cva.stanford.edu