# EFFICIENT MICROARCHITECTURE FOR NETWORK-ON-CHIP ROUTERS

# A DISSERTATION SUBMITTED TO THE DEPARTMENT OF ELECTRICAL ENGINEERING AND THE COMMITTEE ON GRADUATE STUDIES OF STANFORD UNIVERSITY IN PARTIAL FULFILLMENT OF THE REQUIREMENTS FOR THE DEGREE OF DOCTOR OF PHILOSOPHY

Daniel U. Becker August 2012

# © 2012 by Daniel Ulf Becker. All Rights Reserved. Re-distributed by Stanford University under license with the author.

This dissertation is online at: http://purl.stanford.edu/wr368td5072

Includes supplemental files:

- 1. Parameterized Network-on-Chip Router RTL (router.tgz)

- 2. Common RTL Component Library (clib.tgz)

| William Dally, Primary Advise                                                                                                                                             |

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy. |

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Christoforos Kozyrakis**

I certify that I have read this dissertation and that, in my opinion, it is fully adequate in scope and quality as a dissertation for the degree of Doctor of Philosophy.

**Oyekunle Olukotun**

Approved for the Stanford University Committee on Graduate Studies.

Patricia J. Gumport, Vice Provost Graduate Education

This signature page was generated electronically upon submission of this dissertation in electronic format. An original signed hard copy of the signature page is on file in University Archives.

### Abstract

Continuing advances in semiconductor technology, coupled with an increasing concern for energy efficiency, have led to an industry-wide shift in focus towards modular designs that leverage parallelism in order to meet performance goals. Networks-on-Chip (NoCs) are widely regarded as a promising approach for addressing the communication challenges associated with future Chip Multi-Processors (CMPs) in the face of further increases in integration density. In the present thesis, we investigate implementation aspects and design trade-offs in the context of routers for NoC applications. In particular, our focus is on developing efficient control logic for high-performance router implementations.

Using parameterized RTL implementations, we first evaluate representative Virtual Channel (VC) and switch allocator architectures in terms of matching quality, delay, area and power. We also investigate the sensitivity of these properties to key network parameters, as well as the impact of allocation on overall network performance. Based on the results of this study, we propose microarchitectural modifications that improve delay, area and energy efficiency: Sparse VC allocation reduces the complexity of VC allocators by exploiting restrictions on transitions between packet classes. Two improved schemes for speculative switch allocation improve delay and cost while maintaining the critical latency improvements at low to medium load; this is achieved by incurring a minimal loss in throughput near the saturation point. We also investigate a practical implementation of combined VC and switch allocation and its impact on network cost and performance.

The second part of the thesis focuses on router input buffer management. We

explore the design trade-offs involved in choosing a buffer organization, and we evaluate practical static and dynamic buffer management schemes and their impact on network performance and cost. We furthermore show that buffer sharing can lead to severe performance degradation in the presence of congestion. To address this problem, we introduce Adaptive Backpressure (ABP), a novel scheme that improves the utilization of dynamically managed router input buffers by varying the stiffness of the flow control feedback loop based on downstream congestion. By inhibiting unproductive buffer occupancy, this mitigates undesired interference effects between workloads with differing performance characteristics.

# Acknowledgements

First and foremost, I must thank my adviser, Professor William J. Dally, for his support and guidance throughout my career as a graduate student. It has been a privilege to be able to draw on Bill's vast experience and breadth of knowledge, and my research has benefitted greatly from his keen insights and critical feedback over the years.

I would also like to thank the members of my reading committee, Professor Christos Kozyrakis and Professor Kunle Olukotun. I was fortunate to have both as teachers during my first year at Stanford, and I thoroughly enjoyed our interactions as part of the Pervasive Parallelism Lab in recent years. I furthermore thank Professor Yoshio Nishi for serving as the chair for my dissertation defense.

I am grateful to the past and present members of the Concurrent VLSI Architecture group at Stanford for providing a stimulating and fun work environment for the past five years. George Michelogiannakis shared an office with me for most of my time at Stanford and was a dependable comrade-in-arms in the crusade for free food. In addition to fruitful discussions, Curt Harting and Ted Jiang provided for many entertaining Friday evenings in Gates and patiently listened to my venting when the need arose. I also thank our support staff, particularly Uma Mulukutla and Sue George, for working behind the scenes to make our lives easier.

The research leading up to this dissertation would not have been possible without the generous financial support provided by the Professor Michael J. Flynn Stanford Graduate Fellowship. Additionally, I am indebted to the National Science Foundation (Grant CCF-0702341) and the National Security Agency (Contract H98230-08-C-0272-P007) for funding parts of my work.

On a more personal note, I would like to thank the many amazing folks outside of my research area that I have had the opportunity to meet along the way. I am particularly grateful to Emily Deal for all of her support and encouragement over the past three years, and especially for her patience and her help during the final stretch of my PhD; the fact that I have retained a shred of sanity in the process is largely to her credit. Five iterations of the Stanford Men's Volleyball Club team forced me to leave the comfort of my office on a somewhat regular basis and contributed many memorable moments to my Stanford experience. I also thank the Stanford German Student Association for their part in creating a home away from home. Many others have contributed to making the past five years of my life a largely enjoyable experience, and I am grateful to all of them.

Finally and most importantly, I thank my family back home for their unconditional support, their unwavering confidence in my abilities and their encouragement in all of my endeavors—even the ones that put us nine time zones apart. Without you, this journey would not have been possible.

# Contents

| $\mathbf{A}$ | Abstract Acknowledgements |                                |    |  |

|--------------|---------------------------|--------------------------------|----|--|

| $\mathbf{A}$ |                           |                                |    |  |

| 1            | Intr                      | oduction                       | 1  |  |

|              | 1.1                       | Motivation                     | 1  |  |

|              |                           | 1.1.1 Networks-on-Chip         | 2  |  |

|              |                           | 1.1.2 Router Microarchitecture | 4  |  |

|              | 1.2                       | Contributions                  | 7  |  |

|              | 1.3                       | Outline                        | 9  |  |

| 2            | Arb                       | iters                          | 11 |  |

|              | 2.1                       | Overview                       | 11 |  |

|              | 2.2                       | Fixed-Priority Arbiters        | 12 |  |

|              | 2.3                       | Round-Robin Arbiters           | 13 |  |

|              | 2.4                       | Matrix Arbiters                | 16 |  |

|              | 2.5                       | Tree Arbiters                  | 18 |  |

|              | 2.6                       | Multi-Priority Arbiters        | 19 |  |

|              | 2.7                       | Evaluation                     | 20 |  |

|              |                           | 2.7.1 Experimental Setup       | 20 |  |

|              |                           | 2.7.2 Delay                    | 22 |  |

|              |                           | 2.7.3 Area                     | 22 |  |

|              |                           | 2.7.4 Power-Delay Product      | 24 |  |

|              |                           | 2.7.5 Multi-Priority Overhead  | 24 |  |

|   | 2.8  | Related Work                    |

|---|------|---------------------------------|

|   | 2.9  | Summary                         |

| 3 | Allo | ocators 28                      |

|   | 3.1  | Overview                        |

|   | 3.2  | Separable Allocators            |

|   | 3.3  | Wavefront Allocators            |

|   |      | 3.3.1 Fairness                  |

|   |      | 3.3.2 Acyclic Implementations   |

|   | 3.4  | Maximum-Size Allocation         |

|   | 3.5  | Evaluation                      |

|   |      | 3.5.1 Experimental Setup        |

|   |      | 3.5.2 Delay                     |

|   |      | 3.5.3 Area                      |

|   |      | 3.5.4 Power-Delay Product       |

|   |      | 3.5.5 Fairness Overhead         |

|   | 3.6  | Related Work                    |

|   | 3.7  | Summary                         |

| 4 | Vir  | tual Channel Allocation 48      |

|   | 4.1  | Overview                        |

|   | 4.2  | Implementation                  |

|   | 4.3  | Sparse VC Allocation            |

|   | 4.4  | Evaluation                      |

|   |      | 4.4.1 Experimental Setup        |

|   |      | 4.4.2 Matching Quality          |

|   |      | 4.4.3 Network-Level Performance |

|   |      | 4.4.4 Delay and Cost            |

|   | 4.5  | Related Work                    |

|   | 4.6  | Summary                         |

| 5 | Swi | tch Al     | llocation                      | 66  |  |  |

|---|-----|------------|--------------------------------|-----|--|--|

|   | 5.1 | 1 Overview |                                |     |  |  |

|   | 5.2 | Imple      | mentation                      | 67  |  |  |

|   | 5.3 | Specu      | llative Switch Allocation      | 70  |  |  |

|   |     | 5.3.1      | Canonical Speculation          | 71  |  |  |

|   |     | 5.3.2      | Pessimistic Speculation        | 72  |  |  |

|   |     | 5.3.3      | Priority-Based Speculation     | 74  |  |  |

|   | 5.4 | Comb       | pined VC and Switch Allocation | 75  |  |  |

|   | 5.5 | Evalua     | ation                          | 77  |  |  |

|   |     | 5.5.1      | Experimental Setup             | 77  |  |  |

|   |     | 5.5.2      | Matching Quality               | 78  |  |  |

|   |     | 5.5.3      | Network-Level Performance      | 82  |  |  |

|   |     | 5.5.4      | Delay and Cost                 | 86  |  |  |

|   | 5.6 | Relate     | ed Work                        | 92  |  |  |

|   | 5.7 | Summ       | nary                           | 93  |  |  |

| 6 | Buf | fer Ma     | anagement                      | 95  |  |  |

|   | 6.1 |            | riew                           | 95  |  |  |

|   | 6.2 |            | Organization                   | 95  |  |  |

|   |     | 6.2.1      | Number of VCs                  | 96  |  |  |

|   |     | 6.2.2      | Maximum VC Capacity            | 97  |  |  |

|   |     | 6.2.3      | VC Reallocation Policy         | 98  |  |  |

|   | 6.3 | Static     | Buffer Management              | 99  |  |  |

|   | 6.4 | Dynar      | mic Buffer Management          | 100 |  |  |

|   |     | 6.4.1      | Implementation                 | 101 |  |  |

|   |     | 6.4.2      | Overhead                       | 103 |  |  |

|   | 6.5 | Deadl      | ock Avoidance                  | 104 |  |  |

|   | 6.6 | Evalua     | ation                          | 107 |  |  |

|   |     | 6.6.1      | Experimental Setup             | 107 |  |  |

|   |     | 6.6.2      | Cost-Performance Trade-offs    | 108 |  |  |

|   |     | 6.6.3      | Atomic VC Allocation           | 116 |  |  |

|              | 6.7          | Related Work                  | 116 |  |  |  |

|--------------|--------------|-------------------------------|-----|--|--|--|

|              | 6.8          | Summary                       | 117 |  |  |  |

| 7            | Ada          | ptive Backpressure 1          | .19 |  |  |  |

|              | 7.1          | Overview                      | 119 |  |  |  |

|              | 7.2          | Motivation                    | 120 |  |  |  |

|              | 7.3          | Detailed Description          | 124 |  |  |  |

|              |              | 7.3.1 Quota Computation       | 125 |  |  |  |

|              |              | 7.3.2 Implementation          | 130 |  |  |  |

|              |              | 7.3.3 Overhead                | 134 |  |  |  |

|              | 7.4          |                               | 135 |  |  |  |

|              |              |                               | 135 |  |  |  |

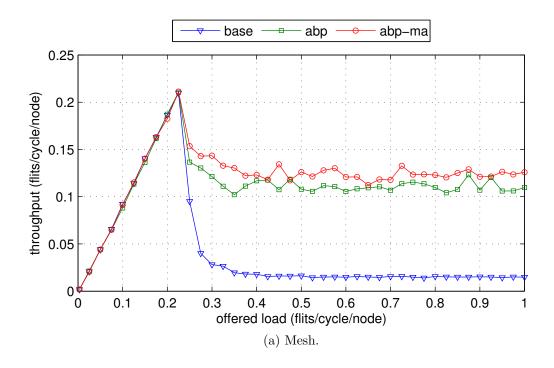

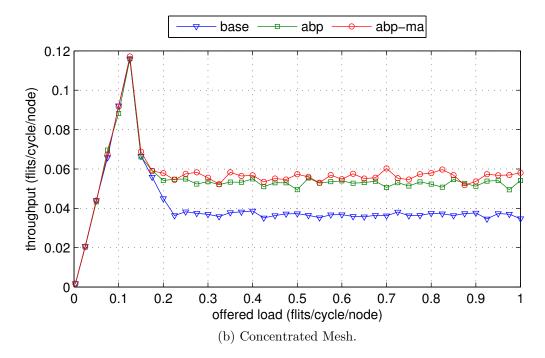

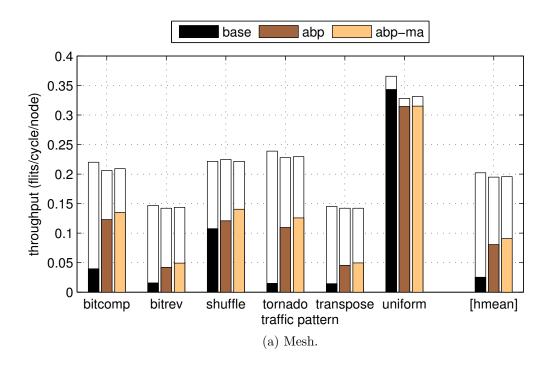

|              |              | 7.4.2 Synthetic Traffic       | 138 |  |  |  |

|              |              | 7.4.3 Application Performance | 147 |  |  |  |

|              | 7.5          |                               | 150 |  |  |  |

|              | 7.6          |                               | 151 |  |  |  |

| 8            | Conclusion 1 |                               |     |  |  |  |

|              | 8.1          | Summary                       | 152 |  |  |  |

|              | 8.2          | Future Work                   | 155 |  |  |  |

| $\mathbf{A}$ | Rou          | ter RTL Overview 1            | .57 |  |  |  |

| Bi           | bliog        | raphy 1                       | 65  |  |  |  |

# List of Tables

| 2.1 | Experimental setup details            | 2.  |

|-----|---------------------------------------|-----|

| 6.1 | Buffer management implementation cost | 103 |

|     | Storage overhead for ABP              |     |

| A.1 | Source tree for router RTL            | 158 |

| A.2 | Design parameters for router RTL      | 159 |

# List of Figures

| 1.1  | Power breakdown for Intel Teraflop Research Chip                          | 4  |

|------|---------------------------------------------------------------------------|----|

| 1.2  | Router microarchitecture overview                                         | 5  |

| 2.1  | Linear implementation of a fixed-priority arbiter                         | 12 |

| 2.2  | Linear implementation of a round-robin arbiter                            | 14 |

| 2.3  | Acyclic implementation of a round-robin arbiter                           | 15 |

| 2.4  | Tree arbiter with $m \times n$ inputs                                     | 17 |

| 2.5  | Dual-priority arbiter                                                     | 19 |

| 2.6  | Minimum delay for $n$ -port arbiter implementations                       | 21 |

| 2.7  | Area-delay trade-off curves for $n$ -port arbiters                        | 23 |

| 2.8  | Power-delay-product for $n$ -port arbiters                                | 25 |

| 2.9  | Cycle time penalty for implementing dual-priority support                 | 26 |

| 3.1  | Separable allocators with $n$ inputs and $m$ outputs                      | 30 |

| 3.2  | Example of inefficiency in separable input-first allocation               | 31 |

| 3.3  | Implementation of a wavefront allocator with $n=4$ ports                  | 33 |

| 3.4  | Circular priority diagonal selection results in uneven distribution of    |    |

|      | grants                                                                    | 34 |

| 3.5  | Acyclic wavefront allocator using unrolling with $n=4$ ports              | 37 |

| 3.6  | Loop-free equivalent wavefront arrays for individual priority selections. | 38 |

| 3.7  | Acyclic wavefront allocator using input/output transformation             | 39 |

| 3.8  | Acyclic wavefront allocator using replication                             | 40 |

| 3.9  | Example of starvation in maximum-size allocation                          | 41 |

| 3.10 | Minimum cycle time for $n$ -port wavefront allocators                     | 43 |

| 3.11 | Area-delay trade-off curves for $n$ -port wavefront allocators            | 44  |

|------|---------------------------------------------------------------------------|-----|

| 3.12 | Power-delay-product for $n$ -port wavefront allocators                    | 46  |

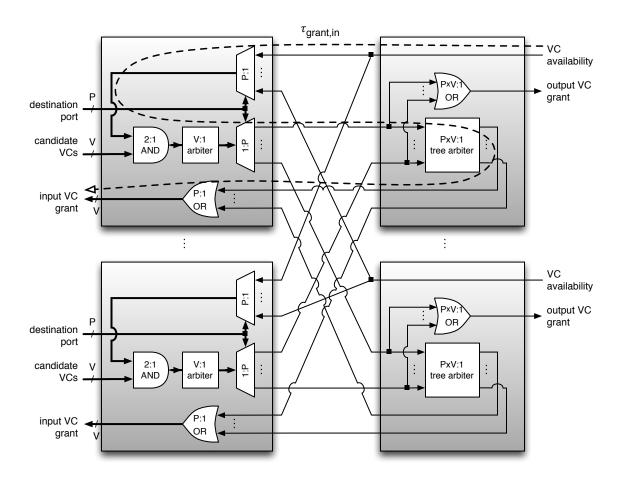

| 4.1  | Separable input-first VC allocator                                        | 50  |

| 4.2  | Separable output-first VC allocator                                       | 51  |

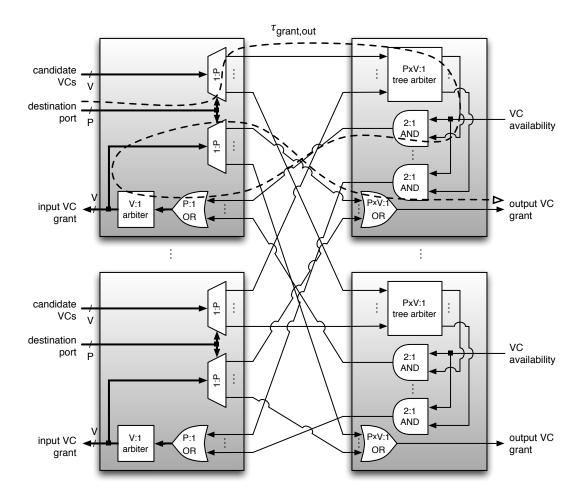

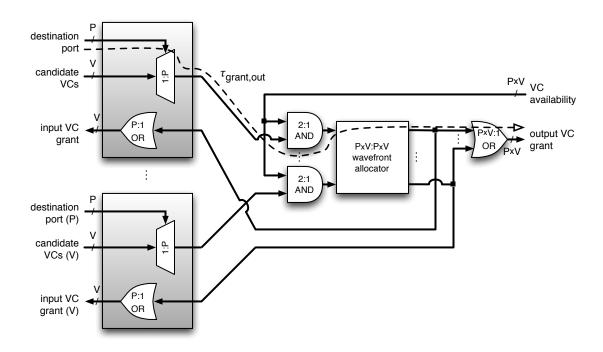

| 4.3  | Wavefront-based VC allocator                                              | 52  |

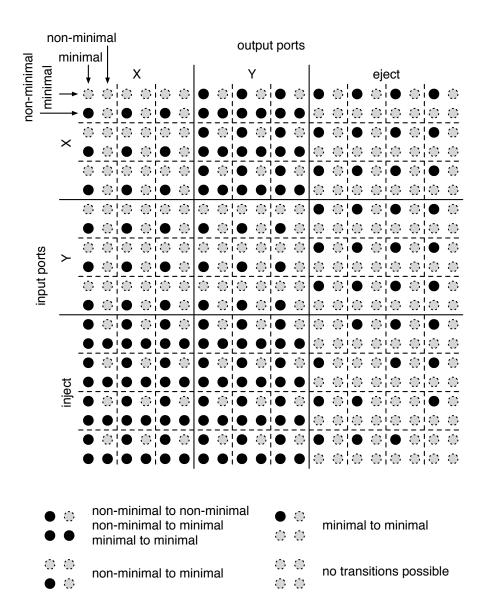

| 4.4  | Legal class transitions for UGAL routing on FBfly networks                | 55  |

| 4.5  | VC allocator matching quality                                             | 58  |

| 4.6  | Impact of VC allocation on saturation throughput (8×8 Mesh, 8 VCs).       | 60  |

| 4.7  | Minimum cycle time for VC allocator implementations                       | 61  |

| 4.8  | Area-delay trade-off for VC allocator implementations                     | 63  |

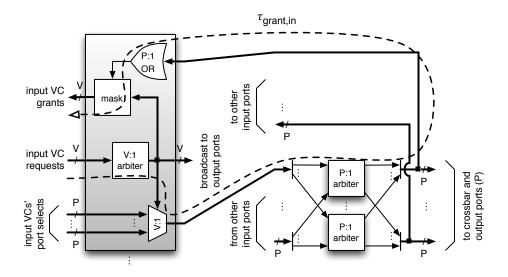

| 5.1  | Separable input-first switch allocator                                    | 68  |

| 5.2  | Separable output-first switch allocator                                   | 69  |

| 5.3  | Wavefront-based switch allocator                                          | 69  |

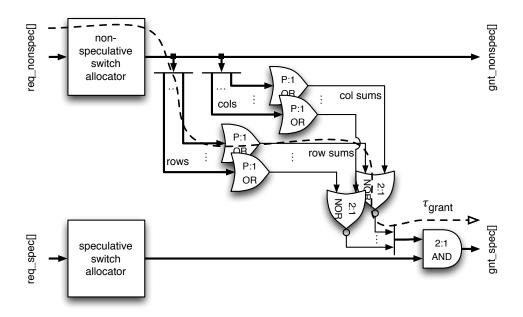

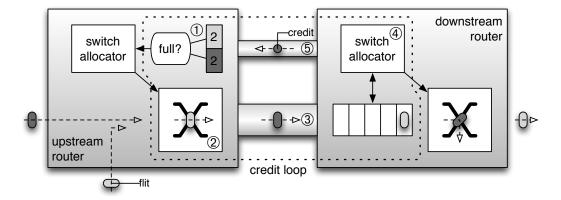

| 5.4  | Canonical implementation of speculative switch allocation                 | 71  |

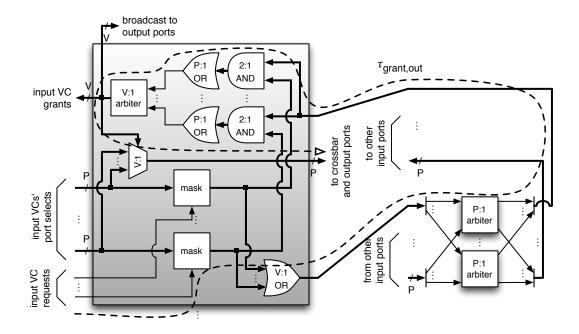

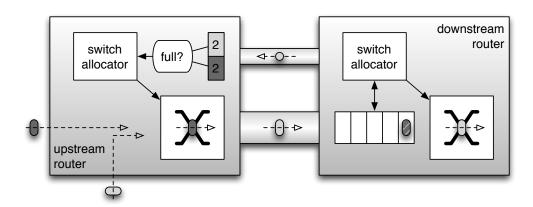

| 5.5  | Pessimistic speculation shortens the critical path                        | 73  |

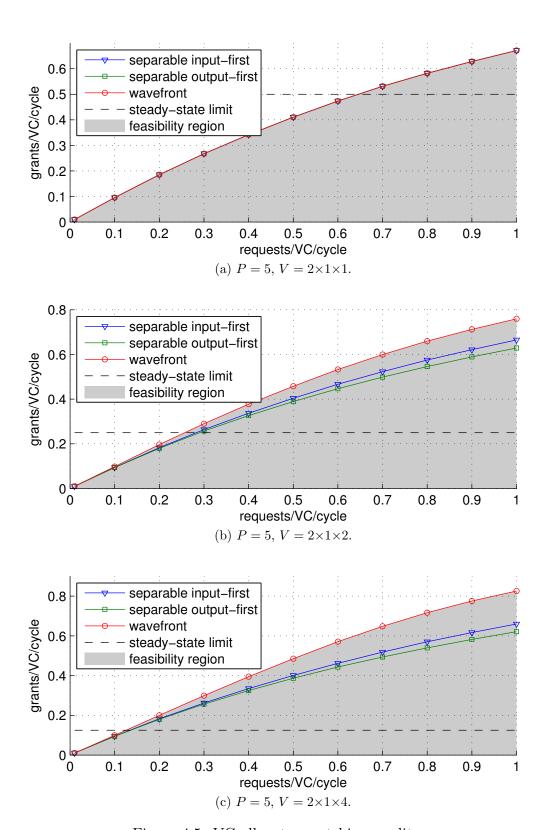

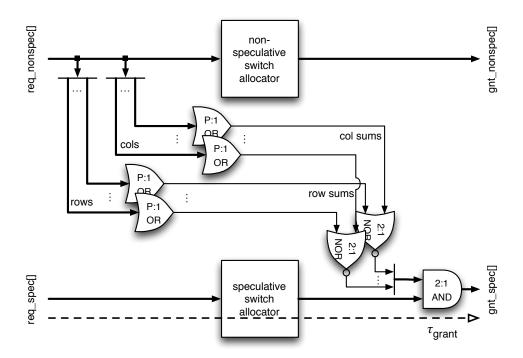

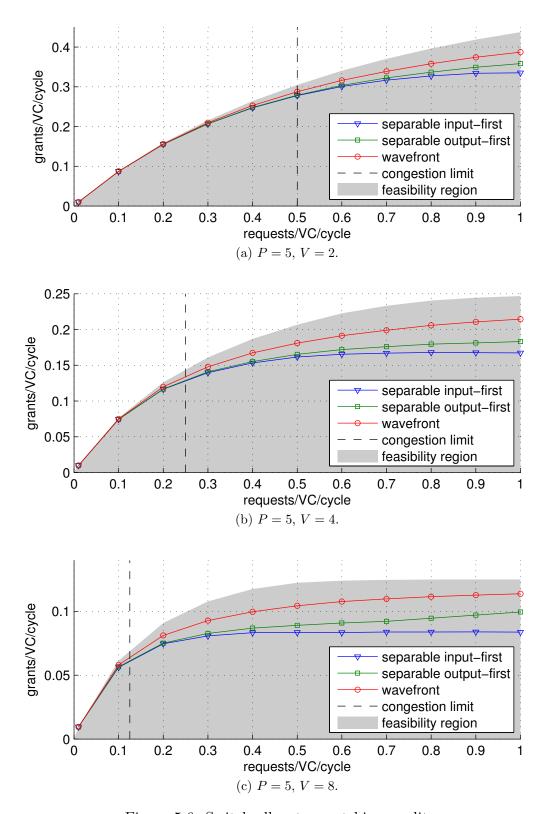

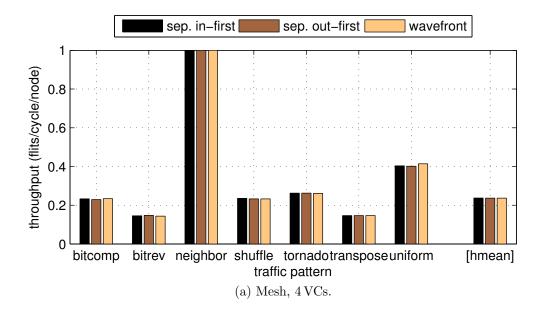

| 5.6  | Switch allocator matching quality                                         | 79  |

| 5.7  | Impact of switch allocation on saturation throughput                      | 81  |

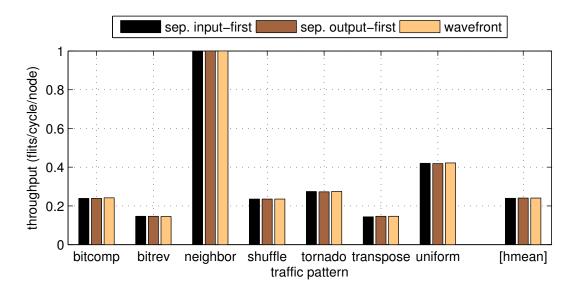

| 5.8  | Impact of speculative switch allocation on packet latency for UR traffic. | 84  |

| 5.9  | Impact of combined allocation on packet latency for Mesh (UR traffic).    | 85  |

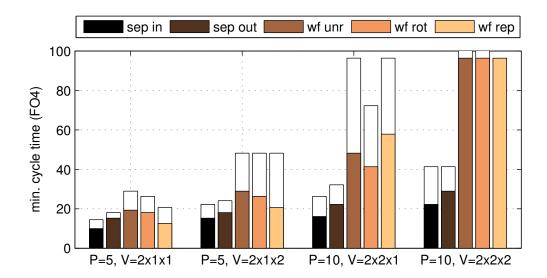

| 5.10 | Minimum cycle time for switch allocator implementations                   | 86  |

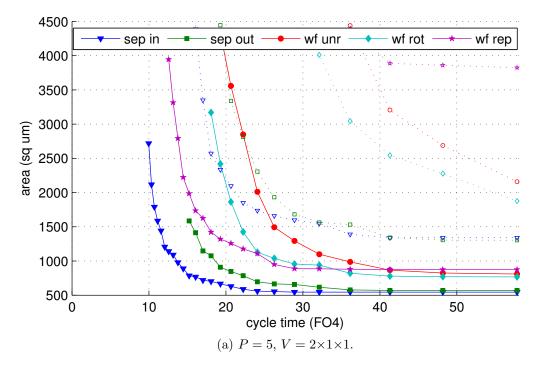

| 5.11 | Area-delay trade-off for switch allocator implementations                 | 87  |

| 5.12 | Minimum cycle time for speculation implementations                        | 88  |

| 5.13 | Area-delay trade-off for speculation implementations                      | 89  |

| 5.14 | Area-delay trade-off for complete router instances                        | 90  |

| 6.1  | Buffer management overhead for a 16-entry buffer                          | 104 |

| 6.2  | Buffer sharing causes interleaving deadlock                               | 105 |

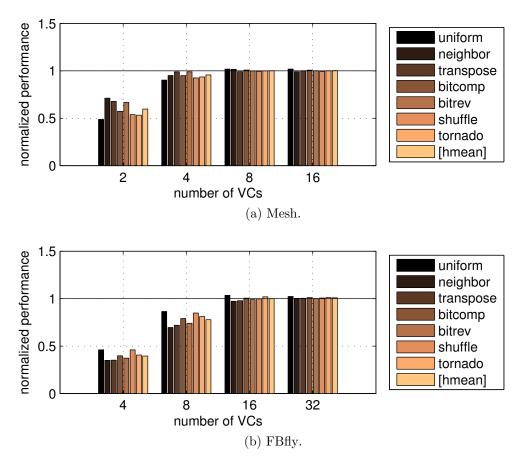

| 6.3  | Cost-performance trade-offs for Mesh                                      | 109 |

| 6.4  | Maximum VC capacity for 16-entry buffer                                   | 112 |

| 6.5  | Zero-load latency for Mesh (16 buffer slots, UR traffic)                  | 112 |

| 6.6  | Cost-performance trade-offs for FBfly (all traffic patterns)            | 113 |

|------|-------------------------------------------------------------------------|-----|

| 6.7  | Performance impact of using atomic VC allocation                        | 115 |

| 7.1  | Unrestricted sharing causes congestion to spread across VCs             | 121 |

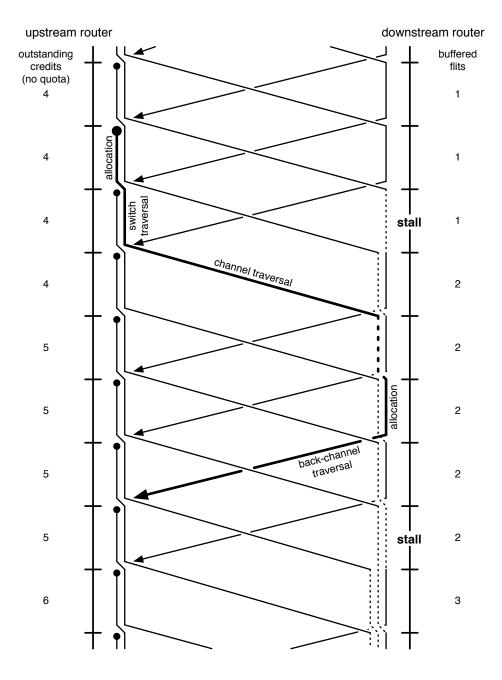

| 7.2  | With no credit quota, congestion causes flits to accumulate downstream. | 126 |

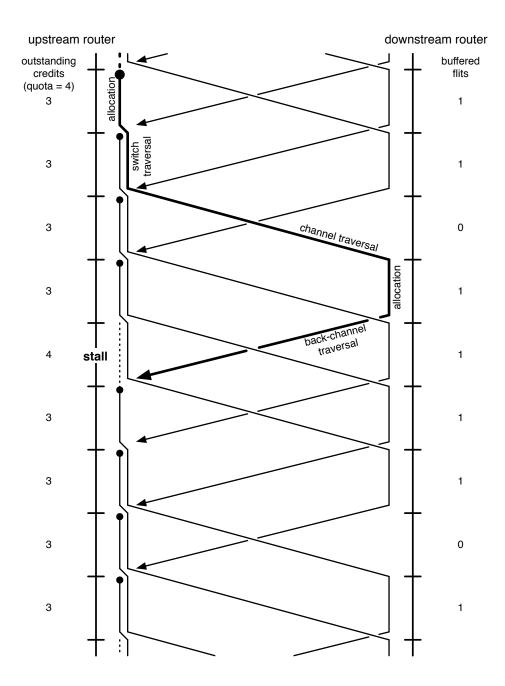

| 7.3  | Limiting credits reduces the effective downstream throughput            | 127 |

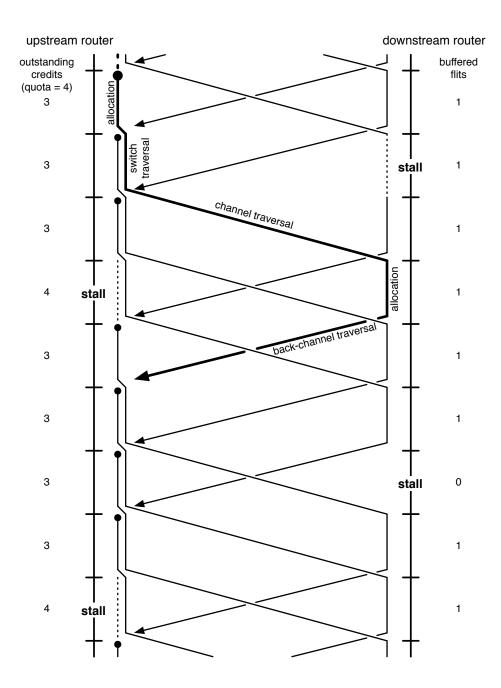

| 7.4  | Matching quotas to congestion levels prevents accumulation of flits     | 129 |

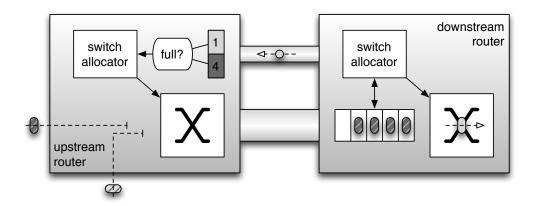

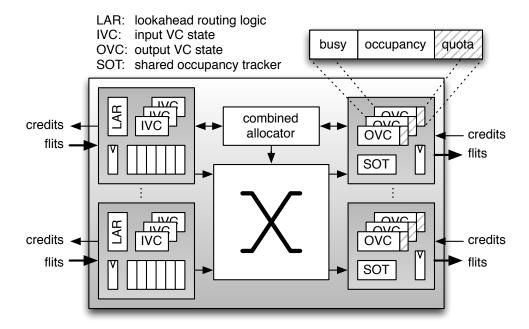

| 7.5  | Router block diagram with modifications for quota enforcement           | 131 |

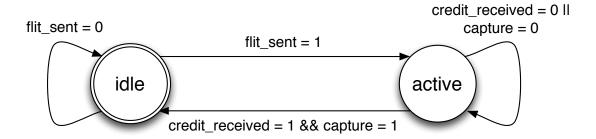

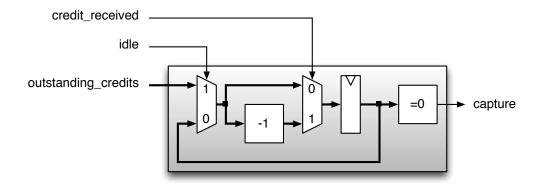

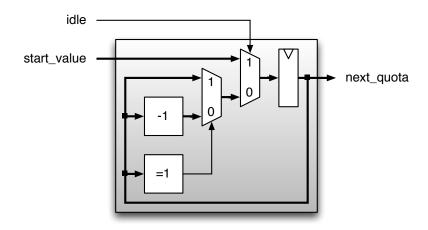

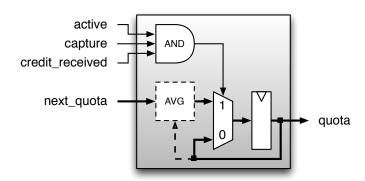

| 7.6  | State transition diagram for quota computation logic                    | 132 |

| 7.7  | Implementation sketches for quota computation logic components          | 133 |

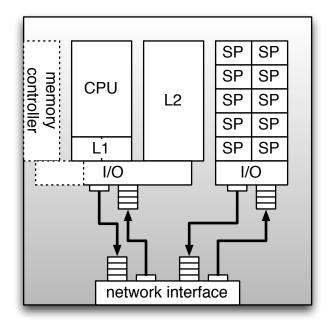

| 7.8  | Target system for CMP application workloads                             | 136 |

| 7.9  | Network node configuration                                              | 137 |

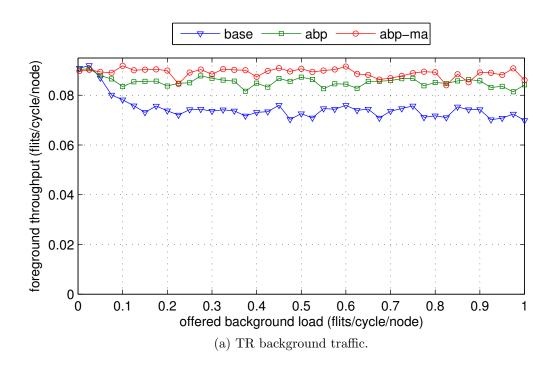

| 7.10 | Throughput vs. offered load for TO traffic pattern                      | 140 |

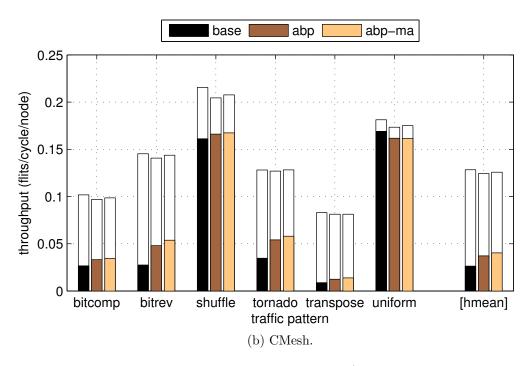

| 7.11 | Throughput at maximum injection rate (outlines show saturation rate).   | 142 |

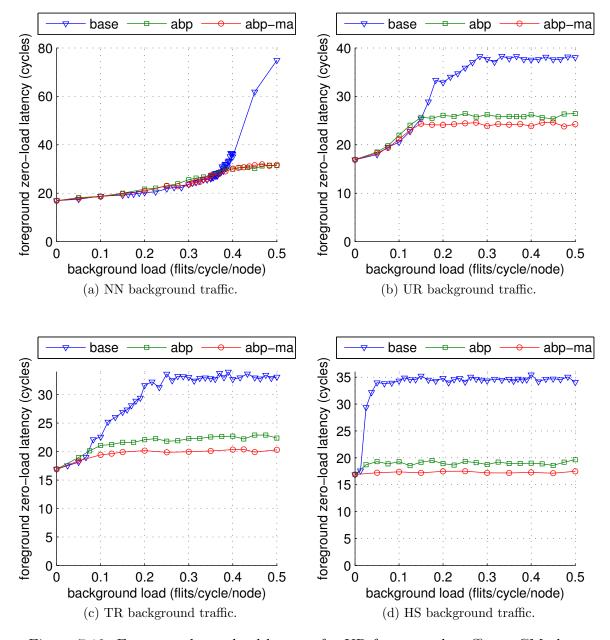

| 7.12 | Foreground zero-load latency for UR foreground traffic on CMesh         | 144 |

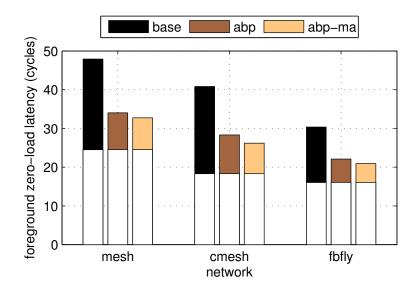

| 7.13 | Average foreground zero-load latency with $50\%$ UR background traffic. | 145 |

| 7.14 | Throughput degradation for UR foreground traffic on CMesh               | 146 |

| 7.15 | Application slowdown for general-purpose cores                          | 148 |

# Chapter 1

### Introduction

### 1.1 Motivation

Continuing advances in semiconductor process technology are providing chip designers with ever increasing transistor budgets. Traditionally, each new process generation has resulted in faster, smaller and more efficient transistors; as a result, designers have historically focused on improving single-threaded performance by means of higher clock speeds and the use of wider and more sophisticated microarchitectures that improve instruction execution rates by attempting to extract increasing amounts of parallelism from a sequential instruction stream. However, with the end of Dennard scaling [22], further clock frequency increases are constrained by practical limits on power dissipation; at the same time, timing overhead and the performance implications of pipeline flushes render further increases in pipeline depth impractical. Finally, superscalar execution techniques have reached a point of diminishing returns as typical instruction streams only offer a limited amount of parallelism that can be extracted at reasonable cost. At the same time, there is substantial demand for continued improvements in processing power. In combination with an increasing concern for energy efficiency driven by the rise of mobile devices, this has led to an industrywide shift in focus towards designs that rely on explicit parallelism to achieve their performance and efficiency goals [2, 13, 69].

In such parallel designs, system performance is defined by the aggregate performance across multiple processing elements, and process scaling is exploited by increasing the number—rather than the complexity—of such elements. Hence, as scaling continues, it becomes necessary to divide a given problem into an increasingly larger number of sub-problems in order to realize continued performance improvements; for a fixed problem size, this generally implies an increase in the amount of communication between processing elements, each of which is responsible for a proportionally smaller slice of the overall problem. With future designs expected to integrate hundreds of processing cores on a single chip, on-chip communication is thus expected to have a significant impact on chip-level performance and energy efficiency [30, 48, 81, 91].

### 1.1.1 Networks-on-Chip

Networks-on-Chip (NoCs) are widely regarded as a promising approach for addressing the communication demands of large-scale Chip Multi-Processors (CMPs) [9,19,33]<sup>1</sup>. Such packet-switched on-chip interconnects are embodied by a set of routers that are connected to each other and to the network endpoints by point-to-point links, and they are characterized by three primary design parameters:

**Topology:** The network topology dictates the number of routers and channels and the connectivity among them. In determining network diameter and bisection bandwidth, it establishes basic bounds for overall network performance and energy efficiency. Furthermore, by controlling the number and size of individual network components, the topology represents a critical factor in determining overall network cost.

Due to the realities of semiconductor manufacturing, NoCs typically favor the use of tiled two-dimensional topologies like the Mesh, Concentrated Mesh (CMesh) [4] or Flattened Butterfly (FBfly) [45].

<sup>&</sup>lt;sup>1</sup> Additionally, compared to traditional approaches that rely on ad-hoc wiring, the use of a structured, packetized interconnect can reduce design complexity and verification effort, as it inherently imposes well-defined module boundaries.

1.1. MOTIVATION 3

Routing: The routing function selects the path that a given packet must take from its source to its destination endpoint. As such, it affects the average hop count and the degree to which load is balanced across network channels, effectively limiting how closely the observed performance and energy efficiency can approach the bounds established by the network topology.

Because of delay and cost constraints, NoCs typically employ simple arithmetic routing functions like Dimension-Order Routing (DOR); i.e., a packet's output port at each router is computed from its destination address and the address of the router.

Flow control: The flow control scheme governs how routers communicate with each other; in particular, it determines when packets—or, in many practical implementations, fixed-size parts of packets called *flits*—can be forwarded from one router to the next. Consequently, flow control regulates resource utilization and thus has a significant impact on performance. In addition, the buffer space requirements imposed by a given flow control scheme directly affect the implementation cost and power consumption of each router.

Most NoC designs employ Virtual Channel (VC) flow control [17,18]; however, recent work has investigated alternative flow control schemes in an effort to reduce buffer overhead [55,60].

While these parameters set the general framework for the network's performance, cost and efficiency, the specific characteristics of a NoC depend on the implementation of its basic components. In particular, routers and network channels set the latency and energy cost incurred for each hop that a packet takes on its way through the network. In addition, the microarchitecture of the routers governs the concrete implementation of the routing algorithm and flow control scheme, determines the behavior in the presence of congestion, and limits the maximum operating frequency; as a result, it directly affects overall network throughput. Finally, the actual implementation cost of the network is clearly defined by the cost of its components.

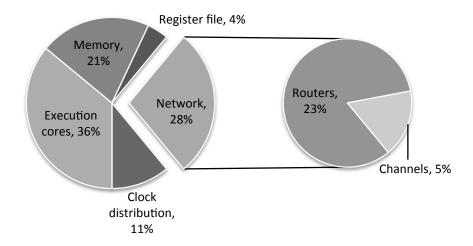

To highlight the importance of developing efficient NoCs, Figure 1.1 shows the power breakdown for the Intel Teraflop Research Chip [39, 95]. This chip comprises

Figure 1.1: Power breakdown for Intel Teraflop Research Chip.

$80 \, \text{tiles}$ —each containing a pair of simple floating point execution units and associated memory arrays—arranged in an  $8 \times 10 \, \text{Mesh}$  with  $38 \, \text{bit}$  wide channels and  $2 \, \text{VCs}$ . When executing a communication-heavy Stencil kernel, the NoC accounts for more than a quarter of the overall chip power;  $83 \, \%$  of the network power is in the routers.

As the number of cores continues to scale up, the impact of the network will become even more pronounced. For example, recent work has found that the underlying  $16 \times 16$  Mesh accounts for 45 % of the total energy expended in performing a  $10^6$ -element radix sort on a cache-coherent 256-node CMP [34].

### 1.1.2 Router Microarchitecture

Developing efficient channels is largely a circuit design problem [14,36,37]; in contrast, a router's performance, cost and efficiency primarily depend on its microarchitecture. The present dissertation investigates implementation aspects and microarchitectural design trade-offs for efficient high-performance NoC routers.

Compared to routers in traditional long-haul and system interconnection networks,

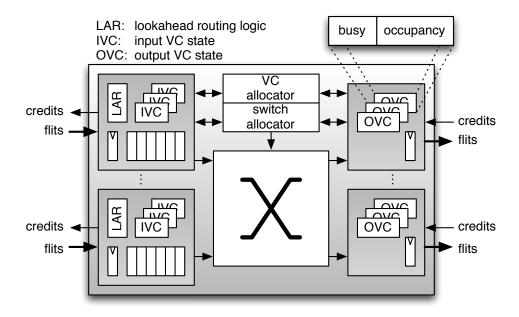

Figure 1.2: Router microarchitecture overview.

NoC routers are subject to markedly different design constraints: As modern semiconductor processes provide an abundant supply of on-chip wiring resources, there is typically no need to use SERDES or sophisticated encoding schemes on the channels. At the same time, performance in CMPs is typically much more sensitive to network latency, mandating both the use of shallow router pipelines and aggressive cycle time targets. Finally, NoCs are generally subject to stringent area and power constraints to avoid interference with the requirements of the network endpoints.

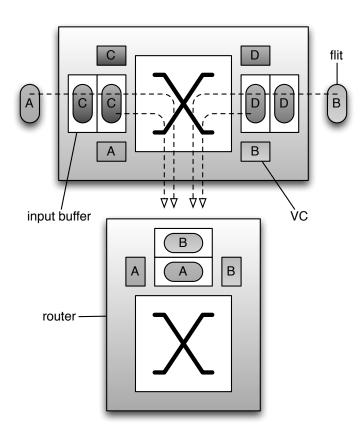

Input-queued routers have emerged as the architecture of choice in current NoC research; in such designs, packets that cannot be forwarded immediately are temporarily held in FIFO buffers at the routers' input ports until they can proceed to the next hop. Buffer space is allocated at the granularity of fixed-size flits, one or more of which comprise a packet, and is logically divided into multiple VCs in order to avoid deadlock and to reduce Head-of-Line (HoL) blocking [17, 18]. Figure 1.2 shows an illustration of a typical NoC router.

A router's primary function is to forward each flit that arrives on one of its inbound channels to an appropriately selected outbound channel. To this end, the following steps must be completed before the flit can depart from its desired output port:

Route computation: The routing logic selects a suitable output port and a set of candidate output VCs for each packet according to the routing algorithm implemented in the network. This step only needs to be performed for the first flit—also termed *head flit*—of each packet; any subsequent flits from the same packet simply inherit the selected output port.

As latency is a critical performance metric in many CMPs, NoC routers commonly implement *lookahead routing* in order to reduce pipeline delay [28].

VC allocation: VC flow control requires each packet to secure exclusive access to an output VC at the selected destination port before flits can be forwarded. The VC allocator assigns available output VCs to waiting packets at the router's input ports. Similar to route computation, VC allocation only needs to be performed for head flits, as the assigned output VC is inherited by subsequent body and tail flits from the same packet.

Switch allocation: Once a packet has been assigned an output port and VC, it can participate in switch allocation. The switch allocator is responsible for establishing a crossbar schedule by assigning time slots to waiting flits at the router's input ports. In particular, it must resolve conflicts between flits destined for the same output port.

**Switch traversal:** Finally, after receiving a grant from the switch allocator, a flit can traverse the router's central crossbar switch in the next cycle to arrive at its destination output and continue its journey through the network.

As in the case of network channels, designing fast and efficient crossbars is primarily a circuit design problem.

Allocators represent a particularly important aspect of router design, as they directly affect overall network performance in several ways: Allocation quality, measured in the cardinality of matchings between requests and available resources, determines the utilization of the router's VCs, the crossbar and the network channels;

as such, it has an immediate impact on the network's throughput under load and on the queuing delay that packets incur in a congested network. Allocators furthermore control the network's fairness properties. Finally, in many typical router designs, allocation directly affects the critical path delay; consequently, delay-optimized allocator implementations are required to enable the network to achieve high operating frequencies.

Prior research has shown that input buffers can account for a significant fraction of a router's overall area and power budget [15,96,98] and that buffer space represents an expensive commodity in the on-chip environment [19,40]; for example, buffers account for 27% of the router power in the Intel Teraflop Research Chip [39]. At the same time, network utilization and performance are highly sensitive to the amount of buffer space that is available to individual packets [17,40,66,80]. Flexible buffer management schemes that yield improvements in buffer utilization represent an attractive approach for reducing buffer cost without sacrificing performance [66,90]. However, in developing such schemes, we must carefully consider any overhead introduced by the buffer management logic itself and avoid undesired side effects on other important characteristics of the network.

Throughout this dissertation, we focus primarily on synthesis-based implementations of router components. This is reflective of recent industry trends, which restrict the use of full-custom logic to critical data path components and large regular structures, particularly memories, in an effort to maximize designer productivity. For example, over the past five generations of IBM POWER and zSeries processors, the fraction of full-custom blocks has shrunk by a factor of ten [27].

### 1.2 Contributions

This dissertation investigates implementation aspects and microarchitectural design trade-offs for efficient high-performance NoC routers. In particular, it makes the following specific contributions:

• We evaluate and compare standard-cell implementations of key router control

logic components in terms of delay, area and energy efficiency in a commercial 45nm process.

- We develop efficient wavefront allocator implementations that avoid combinational cycles, facilitating their use in synthesis-based design flows; our designs improve delay and cost compared to the state-of-the-art implementation described in [43]. We furthermore propose a simple mechanism for alleviating inherent fairness issues in wavefront allocation by modifying the order in which priority diagonals are selected.

- We propose sparse VC allocation, a scheme that reduces the complexity—and hence the delay and cost—of VC allocators by exploiting restrictions on the possible transitions between VCs assigned to different packet classes. In doing so, it increases the router's scalability and facilitates the use of higher-radix network topologies.

- We develop two new implementation variants for speculative switch allocation: Pessimistic speculation takes advantage of the fact that speculative switch allocation is most beneficial at low to medium network load where most requests are granted, while priority-based speculation uses a priority-aware allocator to handle both speculative and non-speculative requests instead of using two separate sub-allocators. Both variants sacrifice some of the performance benefits of speculation near saturation in order to reduce delay and cost compared to the canonical implementation described in [77]; however, they maintain the critical latency benefits under low to medium load.

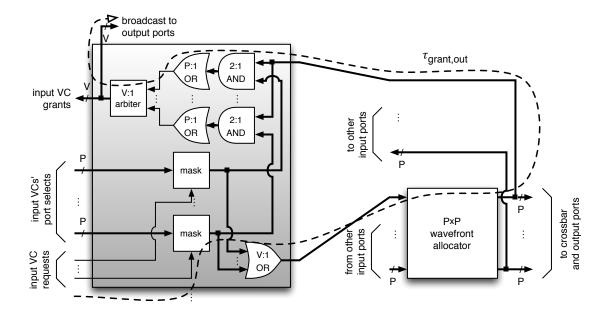

- We describe a practical implementation of combined VC and switch allocation and compare the resulting performance and cost to a canonical router design. Combined allocation yields the same latency improvements as speculative switch allocation at low to medium network load. While allocation inefficiencies lead to slightly reduced throughput near saturation, the cost and delay benefits of avoiding a dedicated VC allocator render combined allocation an attractive design choice for many network configurations.

1.3. OUTLINE 9

We investigate the key trade-offs in the organization and design of router input buffers and evaluate practical buffer management schemes in terms of overhead and performance.

- We identify a performance pathology associated with dynamic buffer management that can lead to undesired interference between multiple traffic classes with different performance characteristics. To address this problem, we develop Adaptive Backpressure (ABP), a novel mechanism that avoids unproductive use of buffer space by regulating credit flow based on observed performance characteristics. We show that ABP can be implemented with minimal changes to the router, and that it effectively mitigates interference without degrading performance under benign load conditions

- Finally, we have developed a parameterized RTL implementation of an NoC router, which we have released to the research community as open source. In addition to facilitating detailed evaluations of implementation trade-offs for the present dissertation, the router has since found use in a number of other research efforts at Stanford and beyond [10, 11, 44, 53, 55, 56, 59, 63, 64, 72, 73].

Parts of our work on VC and switch allocator implementations were previously published in [7]; the work on ABP has been accepted for publication in [8].

### 1.3 Outline

The remainder of this dissertation is organized as follows:

Chapter 2 discusses elementary arbiter designs. We investigate different arbiter types, discuss approaches for providing fairness, scalability and support for multiple priority levels, and evaluate delay and cost in a commercial standard-cell design flow.

Chapter 3 similarly investigates allocators. In particular, our focus is on wavefront allocators: We develop a scheme to alleviate inherent fairness issues in wavefront allocation, and we propose several synthesis-friendly implementation variants that improve delay and cost compared to a state-of-the-art design.

In Chapter 4, we discuss how the basic allocator designs described in Chapter 3 can be used to implement VC allocation. We give an overview of practical implementation variants, describe sparse VC allocation, and present detailed evaluation results for delay, cost and performance.

Chapter 5 analogously addresses the application of elementary allocator designs in the implementation of practical switch allocators. We describe and evaluate exemplary architectures. Furthermore, we discuss speculative switch allocation, and we suggest two implementation variants that improve delay and cost over the canonical design. Finally, we describe and evaluate a practical implementation of combined VC and switch allocation.

Chapter 6 explores trade-offs in input buffer organization and examines state-ofthe-art static and dynamic buffer management schemes. We compare the individual schemes in terms of implementation overhead, discuss deadlock avoidance considerations and evaluate cost-performance trade-offs.

In Chapter 7, we show that dynamic buffer management can lead to severe performance degradation and undesired interference between different traffic classes in the presence of congestion. We develop ABP to mitigate this effect, and we present simulation results both for synthetically generated traffic and for application traffic on a heterogeneous CMP to demonstrate its efficacy.

To conclude the dissertation, Chapter 8 summarizes our contributions and briefly outlines opportunities for future work.

Finally, Appendix A provides a brief overview of the parameterized router RTL that was developed as part of the work described in this dissertation.

# Chapter 2

## Arbiters

### 2.1 Overview

Mediating access to a shared resource between multiple agents is one of the fundamental operations performed by the control logic in a router. We refer to the act of coordinating access in this way as *arbitration*, and to the logic that performs this function as an *arbiter*.

Formally, we can describe the process of arbitration among n agents as a vector operation  $\Phi$  on a binary request vector  $R = \{r_0, r_1, \dots, r_{n-1}\}$  that produces a grant vector  $G = \{g_0, g_1, \dots, g_{n-1}\}$  whose elements satisfy certain properties:

$$G = \Phi(R) \tag{2.1}$$

$$g_i \Rightarrow r_i$$

(2.2)

$$g_i \Rightarrow \bigwedge_{j \neq i} (\neg g_j) \tag{2.3}$$

Equation 2.2 requires that the generated grant vector be consistent with the request vector; i.e., only those agents that actually issued a request in the first place can receive a grant. Equation 2.3, on the other hand, ensures that in case of conflict, only a single agent receives a grant.

While not strictly required, most practical arbiters generate grant vectors that

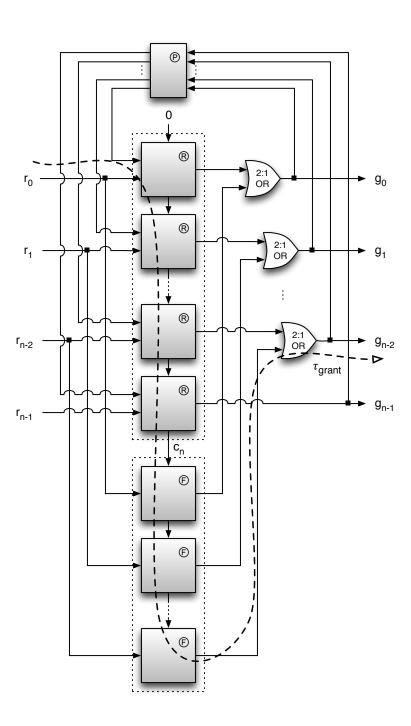

Figure 2.1: Linear implementation of a fixed-priority arbiter.

satisfy an additional property:

$$\bigvee_{i} r_{i} \Rightarrow \bigvee_{i} g_{i} \tag{2.4}$$

That is, if one or more agents request access to the shared resource, one of them will receive a grant. We can take advantage of this property to simplify logic in cases where we need to know whether a resource was granted, but not which particular agent it was granted to.

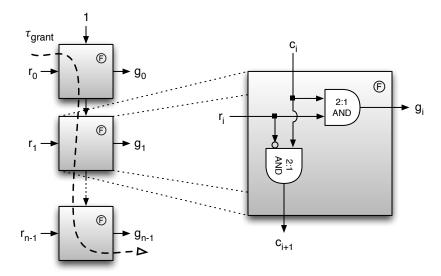

### 2.2 Fixed-Priority Arbiters

This simplest form of arbiters grants access to a shared resource based on a predetermined priority order. If the request inputs are sorted in descending priority order, solving this problem is equivalent to finding the first set bit in a bit vector. Figure 2.1 shows a straightforward implementation using a linear array of basic bit cells  $\widehat{\mathbb{F}}$ , each of which generates a grant  $g_i$  if both its request input  $r_i$  and the incoming priority signal  $c_i$  are asserted. In addition, the incoming priority signal is propagated to the next cell only if  $r_i$  is not asserted. This design minimizes hardware complexity; however,

its critical path delay  $\tau_{grant}$  scales linearly with the number of inputs, as indicated by the dashed arrow in Figure 2.1.

If a large number of inputs must be supported, we can improve delay by taking advantage of the fact that the logic equations for the  $g_i$  and  $c_{i+1}$  outputs are structurally similar to those for a binary half adder's sum and carry outputs, respectively. As such, it is possible to transform the design shown in Figure 2.1 into an equivalent prefix network that hierarchically computes propagation conditions for the initial priority signal, causing the delay to scale logarithmically with the number of inputs.

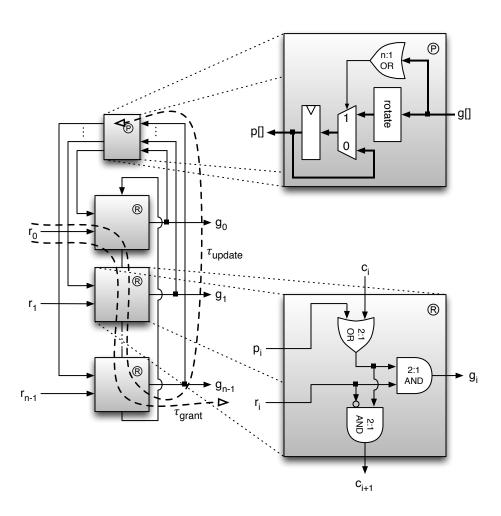

### 2.3 Round-Robin Arbiters

Fixed-priority arbiters require that there be a clear, pre-established priority order among requests. However, in the context of routers, we frequently encounter situations where undifferentiated agents compete for access to a shared resource. In such cases, we are generally interested in maintaining a degree of fairness among the agents: At a minimum, we want to ensure that every request is granted eventually (weak fairness); ideally, though, grants should be distributed equitably among agents (strong fairness).

The round-robin arbiter shown in Figure 2.2 extends the fixed-priority scheme from Section 2.2 by adding a priority select input  $p_i$  to each bit cell  $\mathbb{R}$  and wrapping around the last bit cell's priority output  $c_n$  to the first one's priority input  $c_0$ . The priority select inputs are driven by a state register that contains the most recent grant, rotated by one bit position<sup>1</sup>. Thus, every time a grant is generated, the next agent in line after the one being granted becomes the highest-priority request in the next cycle; this scheme provides strong fairness.

The priority mechanism introduces an additional timing arc  $\tau_{update}$ , as shown in Figure 2.2. Depending on the timing constraints for the grant outputs  $g_i$ , either  $\tau_{update}$  or  $\tau_{grant}$  may represent the critical path for a given arbiter instance.

<sup>&</sup>lt;sup>1</sup> For large arbiters, it is often preferable to reduce overhead by storing this value in binary-encoded form if delay constraints permit.

Figure 2.2: Linear implementation of a round-robin arbiter.

Figure 2.3: Acyclic implementation of a round-robin arbiter.

Commercially available timing analysis tools are typically unable to properly analyze circuits that contain combinational loops like the one generated by wrapping around the priority signals. This is particularly problematic when using a standard cell design flow, as it prevents synthesis from performing proper gate sizing. We can avoid the combinational loop by severing the wraparound priority signal and connecting it to a chain of fixed-priority cells  $\widehat{\mathbb{F}}$  as shown in Figure 2.3<sup>2</sup>. In a naïve implementation, doing so nearly doubles the grant generation delay  $\tau_{grant}$ ; however, in practice, the associated delay penalty can be minimized by computing the intermediate grant signals for the block of  $\widehat{\mathbb{R}}$ -type cells and the block of  $\widehat{\mathbb{F}}$ -type cells in parallel and conditionally selecting either set of grants based on the value of the first block's final priority output  $c_n^3$ . As in the case of fixed-priority arbitration, we can further improve delay by replacing the blocks of  $\widehat{\mathbb{R}}$ -type and  $\widehat{\mathbb{F}}$ -type cells with prefix networks. Alternatively, it is possible to implement the entire round-robin arbiter as a single acyclic prefix network; Dimitrakopoulos et al. describe such a design in detail in [23].

### 2.4 Matrix Arbiters

Matrix arbiters represent another implementation alternative for providing strong fairness. This is achieved by explicitly tracking pairwise precedence between all request inputs and updating it in response to grants in a way that implements a least-recently-served policy. Specifically, for every pair of inputs i and j, the precedence indicator  $p_{i,j}$  determines whether a pending request from input i has higher priority than a pending request from input j. The precedence indicators are stored in a matrix of registers that lends this type of arbiter its name<sup>4</sup>. Any time an input k is granted, it assumes lowest priority by setting  $p_{i,k}$  and resetting  $p_{k,j}$  for all i and j.

Using the precedence values, the grant signal  $g_k$  for a given agent k can thus be

<sup>&</sup>lt;sup>2</sup> Because priority selection never causes  $r_{n-1}$  to be skipped, it does not require an  $\widehat{F}$ -type cell.

<sup>&</sup>lt;sup>3</sup> We will use a similar approach to implement multi-priority arbitration in Section 2.6.

<sup>&</sup>lt;sup>4</sup> Only the upper triangle of the matrix actually requires registers, as  $p_{i,j} = \neg p_{j,i}$  and  $p_{i,i} = 0$ .

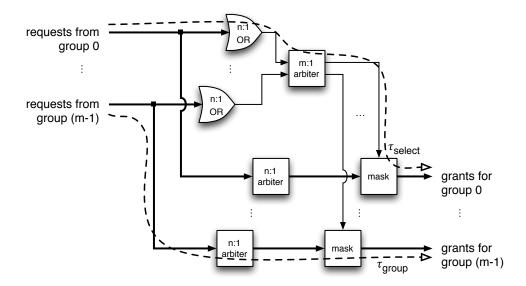

Figure 2.4: Tree arbiter with  $m \times n$  inputs.

computed using a simple reduction tree:

$$g_k = r_k \land \neg \bigvee_{i \neq k} (r_i \land p_{i,k}) \tag{2.5}$$

The associated grant generation delay  $\tau_{grant}$  grows logarithmically with the number of inputs. However, updating the precedence values involves fanout from each grant signal to  $2 \times n$  registers, leading to a larger update delay  $\tau_{update}$  compared to a comparable round-robin arbiter. Furthermore, the number of registers required to hold the precedence matrix—a primary factor in the allocator's implementation cost—exhibits quadratic scaling<sup>5</sup>. As a result, this scheme is typically only attractive for arbiters with a relatively small number of inputs.

### 2.5 Tree Arbiters

In many applications that require large arbiters, the requesting agents are logically organized into multiple groups. In such cases, a single arbiter as described in the preceding two sections distributes grants evenly to all requesting agents regardless of which group they fall into. However, in practice, it is typically preferable to first distribute grants fairly among the different groups and then among the individual agents within each group. This can be achieved using a hierarchical organization of smaller arbiters as shown in Figure 2.4: An  $m \times n$ -input tree arbiter uses m independent n-input arbiters of arbitrary type to determine a winning agent for each individual group; in parallel, a single m-input arbiter selects a winner among all groups that have at least one request and enables only that group's outputs.

If the number and size of groups in a tree arbiter is optimized to match the delay along the two timing arcs  $\tau_{select}$  and  $\tau_{group}$  shown in Figure 2.4, it can achieve lower delay than a monolithic arbiter with the same number of ports. Additionally, for matrix arbiters, tree organization can significantly reduce area and power compared to a monolithic implementation; in particular, implementing an n-input arbiter as l levels of m-input matrix arbiters with  $m = \sqrt[k]{n}$  reduces the total number of registers required by a factor of m compared to a monolithic n-input matrix arbiter<sup>6</sup>.

We can construct tree arbiters with more than two levels by recursively implementing the individual m- and n-input arbiters in Figure 2.4 as tree arbiters themselves. For such multi-level tree arbiters, it is typically beneficial to combine the group enable signals across the levels of the tree and to perform a single stage of masking after the last level, rather than performing individual masking steps after each individual level.

Figure 2.5: Dual-priority arbiter.

### 2.6 Multi-Priority Arbiters

Many applications in which arbiters are used call for the ability to dynamically prioritize a subset of requests that satisfy certain criteria over other requests. E.g., as we shall see in Chapter 5, a speculative switch allocator prioritizes requests from packets that have completed Virtual Channel (VC) allocation over those from packets that have not yet been assigned an output VC.

In many such instances, only a small number of distinct priority levels is required; this enables us to implement multi-priority arbitration by replicating the arbiter frontend—i.e., the part of the arbiter that is responsible for computing grant signals—and masking the intermediate grants generated by the individual front-end instances based on the presence of higher-priority requests as illustrated in Figure 2.57. Masking outputs in this way ensures that only a single request across all priority levels can receive a grant, while sharing the arbiter state among all front-end instances reduces hardware overhead.

<sup>&</sup>lt;sup>5</sup> In particular, a total of  $\frac{n(n-1)}{2}$  registers are required for an *n*-input matrix arbiter.

<sup>6</sup> Note that the *l*-level tree comprises a total of  $\frac{n-1}{m-1}$  *m*-input matrix arbiters.

$<sup>^{7}</sup>$  We assume here that the individual arbiters satisfy Equation 2.4.

While this approach can support a small number of priority levels with comparatively little area and delay overhead, it is impractical for applications that require fine-grained priorities. Such applications fall outside the scope of the present contribution.

### 2.7 Evaluation

In this section, we evaluate the efficiency of the different types of arbiters discussed in the present chapter. To this end, we develop parameterized RTL implementations and synthesize them in a commercial standard-cell design flow. In particular, we consider three different implementations:

**Round-robin:** An acyclic round-robin arbiter as described in Section 2.3, with prefix networks used in place of the two chains of bit cells and conditional grant selection.

**Prefix:** An implementation using a single acyclic prefix networks as described by Dimitrakopoulos et al. [23].

Matrix: A matrix arbiter as described in Section 2.4.

To evaluate scaling behavior, we compare instances of each type of arbiter with five, eight and ten ports. These sizes were chosen to be reflective of typical and large arbiters in Networks-on-Chip (NoCs), respectively. Situations in which arbitration among more than ten agents is necessary typically call for the use of tree arbiters.

### 2.7.1 Experimental Setup

For each configuration, we sweep the target clock frequency under worst-case process conditions and report the resulting cell area, as well as the Power-Delay Product (PDP) assuming a 50% activity factor at all request inputs. The latter quantity represents a measure of the amount of energy that is expended in each round of arbitration. We begin each sweep at a base frequency of  $1.0\,\mathrm{GHz}$  and add  $100\,\mathrm{MHz}$

| Design Compiler version   | G-2012.06         |

|---------------------------|-------------------|

| Target library            | TCBN45GSBWP       |

| FO4 delay                 | $34.6\mathrm{ps}$ |

| Driving / receiving cells | INVD8BWP          |

Table 2.1: Experimental setup details.

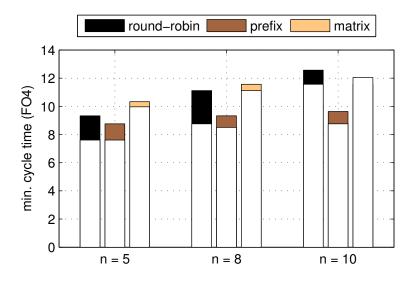

Figure 2.6: Minimum delay for n-port arbiter implementations.

increments until a timing violation is reported. We convert all clock frequencies into their corresponding cycle times and normalize them to the FO4 delay for our target library.

Synthesis is performed using the Synopsys Design Compiler Reference Methodology, targeting a general-purpose library in the TSMC 45GS process. We disable Design-for-Test (DFT) synthesis and enable dynamic power optimization, but otherwise use the default parameters specified by the reference methodology. Arbiter inputs and outputs are connected to standard library inverter cells to ensure realistic drive strength and load, respectively. Table 2.1 provides additional details.

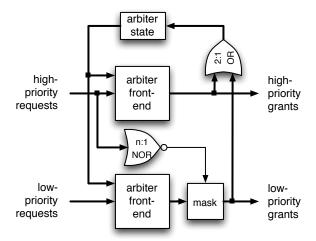

#### 2.7.2 Delay

Contrary to popular wisdom, the synthesis results shown in Figure 2.6 indicate that the minimum cycle time at which a matrix arbiter with a given number of ports can operate exceeds that of both the round-robin arbiter and the prefix arbiter by 30 % in the five- and eight-port configurations. The state update logic represents the critical timing path in each case, and the matrix arbiter is penalized by the large fanout involved in updating the precedence matrix, as mentioned in Section 2.4.

With ten ports, the minimum delay for the round-robin arbiter increases substantially, reducing the difference to the matrix arbiter to 3%; in contrast, the prefix implementation increases its speed advantage even further at this design point.

#### 2.7.3 Area

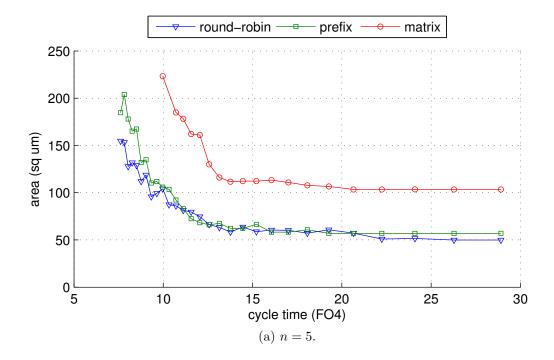

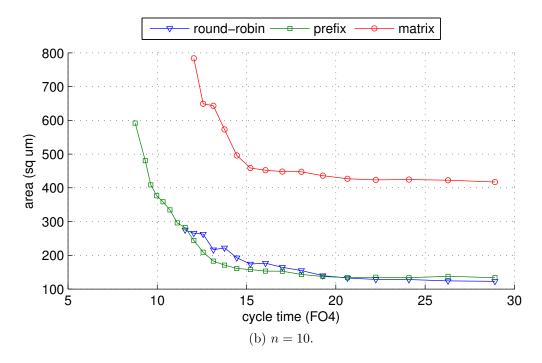

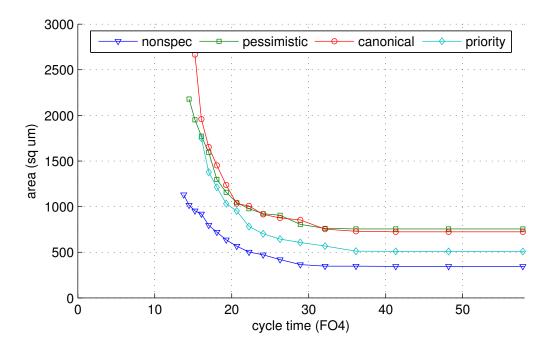

Figure 2.7 shows the trade-off between cell area and cycle time for the three types of arbiters. We omit detailed results for n = 8 for brevity; they are consistent with our observations for the two remaining design points.

At the beginning of the sweep, corresponding to the right side of the figure, all three designs are able to satisfy the timing requirements using minimum-size gates. As a result, area initially remains flat as frequency increases. The knee in each curve indicates the maximum operating frequency that a minimum-size implementation can support; as the target frequency increases beyond this point, synthesis must make use of larger standard cells with increased drive strength in order to be able to satisfy the tighter delay requirements, leading to a rapid increase in overall cell area.

Across both design points, the round-robin and prefix network arbiters both yield lower minimum delay and require less area. This difference is primarily a result of the relatively large number of registers required for implementing a matrix arbiter. Comparing the results for n = 5 and n = 10 at low clock frequencies clearly illustrates the differences in scaling behavior between the round-robin and prefix arbiters (linear scaling) on the one hand and the matrix arbiter (quadratic scaling) on the other hand. The difference in cell area between the round-robin and prefix arbiters is relatively small; the former produces slightly more compact designs at lower target frequencies

Figure 2.7: Area-delay trade-off curves for n-port arbiters.

and for small arbiters, while the latter becomes more efficient as the number of ports increases.

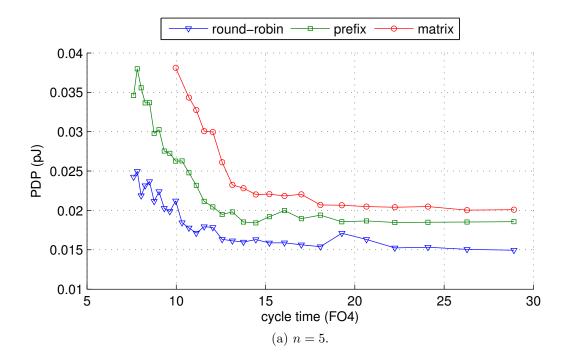

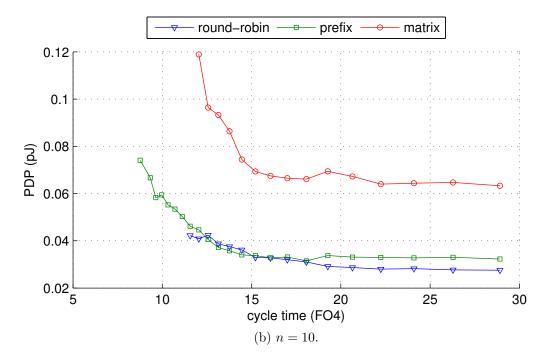

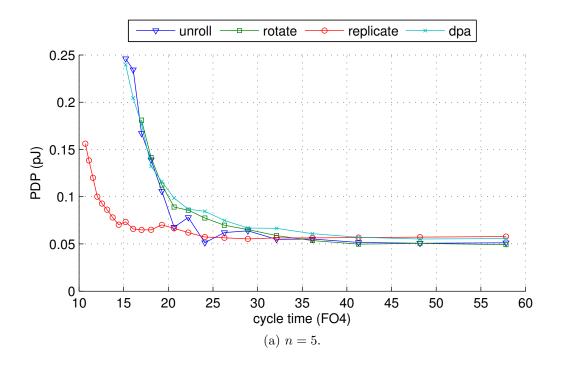

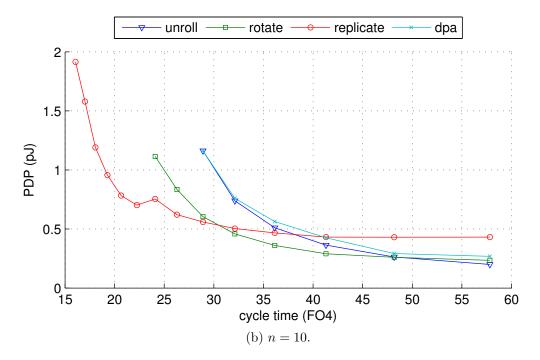

#### 2.7.4 Power-Delay Product

The PDP values, shown in Figure 2.8, largely mirror the results for cell area: Matrix arbiters consistently incur higher energy cost than both other types of arbiters, round-robin arbiters are more efficient for small configurations, and prefix arbiters become more efficient as the number of ports increases. However, compared to the area results, the differences between the round-robin and prefix arbiters are slightly more pronounced, while the differences between those two and the matrix arbiters have become less pronounced. Nevertheless, round-robin arbiters remain the most efficient choice for small configurations, and prefix network arbiters maintain their benefits for large configurations.

### 2.7.5 Multi-Priority Overhead

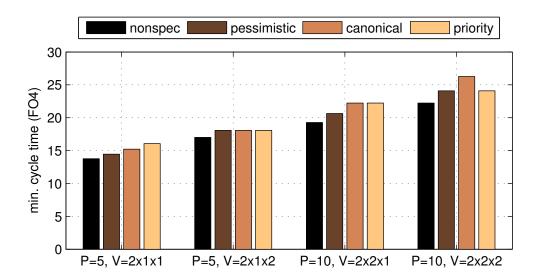

Figure 2.9 illustrates the impact that adding support for two priority levels as described in Section 2.6 has on the minimum cycle time. The white segment at the bottom of each bar corresponds to the minimum cycle time for the single-priority case from Figure 2.6.

The delay increase is most pronounced for the round-robin arbiter and least significant for the matrix arbiter; in the latter case, priority selection can be overlapped with existing logic to a large extent, minimizing the impact on the critical path. With ten inputs, this allows the matrix arbiter to achieve lower cycle times than the dual-priority round-robin arbiter. However, the prefix arbiter remains the fastest implementation across all configurations.

While both area and PDP increase in magnitude when adding dual-priority support, the overall trends remain the same as with a single priority level, with the difference in efficiency between matrix arbiters on the one hand and round robin and prefix arbiters on the other hand decreasing slightly for the larger configurations. We omit the corresponding figures in the interest of brevity.

Figure 2.8: Power-delay-product for n-port arbiters.

Figure 2.9: Cycle time penalty for implementing dual-priority support.

## 2.8 Related Work

Pankaj and McKeown [71] provide detailed block-level descriptions of basic arbiter implementations used in the context of the *Tiny Tera* research project. Huang et al. [41] describe fast full-custom implementations. Preußer et al. [79] develop techniques for using high-speed adder designs to implement arbitration; this approach is of particular benefit for applications that target Field-Programmable Gate Arrayss (FPGAs), which often provide delay-optimized adder blocks that yield better performance than general-purpose programmable logic. Dimitrakopoulos et al. [23] propose a fast arbiter design based on prefix networks. Lee at al. [51] develop a multi-priority arbiter that treats priorities in a *probabilistic*—rather than absolute—manner; i.e., priorities determine the statistical distribution of grants instead of imposing a strict order among requests. Their design has applications in improving global fairness in the network. Finally, Shin et al. [86] present a tool that can generate synthesizable arbiter implementations with arbitrary numbers of inputs.

2.9. SUMMARY 27

## 2.9 Summary

In this chapter, we have presented a brief overview of arbitration and provided detailed descriptions of representative arbiter implementations, which will we will use as building blocks for more complex structures in subsequent chapters. A comparison of standard-cell arbiter implementations in terms of delay, area and energy efficiency shows that—contrary to popular wisdom—matrix arbiters are both less efficient and slower than round-robin arbiters at sizes commonly encountered in NoC routers. Throughout the remainder of this dissertation, we will therefore consider the latter type of arbiter exclusively.

# Chapter 3

# Allocators

## 3.1 Overview

Where arbitration addresses the problem of coordinating access to a single shared resource between multiple competing agents, *allocation* extends the problem to situations where agents compete for multiple resources simultaneously. Specifically, given a set of resources and a set of agents, each of which can request access to one or more of the former, an *allocator* grants resources to agents subject to three basic constraints<sup>1</sup>:

- Resources are only granted to agents that requested them.

- Each agent is granted access to at most one resource.

- Each resource is granted to at most one agent.

Similar to the approach taken in Chapter 2, we can thus formally describe allocation as an operation  $\Psi$  on a two-dimensional binary request matrix  $R = \{r_{i,j}\}$  that produces

<sup>&</sup>lt;sup>1</sup> We also refer to the agents as the allocator's inputs, and to the resources as its outputs; both terms are used interchangeably in the remainder of this dissertation.

a grant matrix  $G = \{g_{i,j}\}$  with the following properties:

$$G = \Psi(R) \tag{3.1}$$

$$g_{i,j} \Rightarrow r_{i,j}$$

(3.2)

$$g_{i,j} \Rightarrow \bigwedge_{k \neq j} (\neg g_{i,k}) \tag{3.3}$$

$$g_{i,j} \Rightarrow \bigwedge_{k \neq i} (\neg g_{k,j}) \tag{3.4}$$

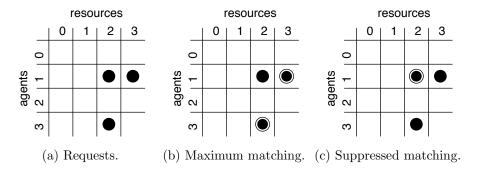

Any grant matrix that satisfies these constraints is called a *matching*. The *cardinality* of a matching is the number of generated grants; it represents a metric for matching quality. We refer to matchings in which no further resource can be granted except by replacing another existing grant as *maximal*. Among these, the matchings with the highest possible cardinality are called *maximum* matchings.

In order to maximize resource utilization, it is desirable for an allocator to produce matchings with the highest possible cardinality. In practice, however, there is a trade-off between matching quality on the one hand and delay, area and power constraints that limit the allocator's logic complexity on the other hand. The remainder of this section discusses allocator implementations that represent different trade-offs between these two qualities.

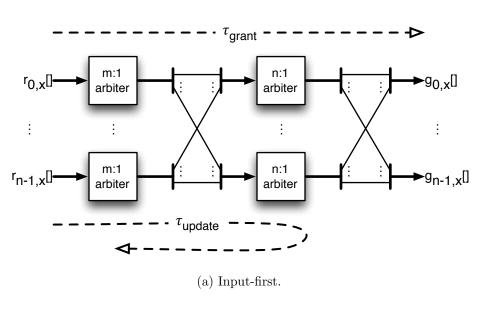

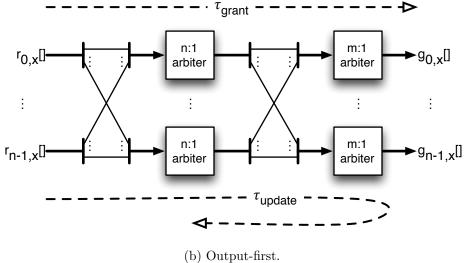

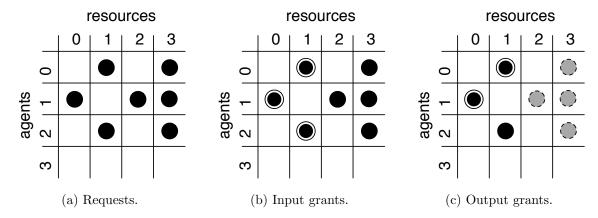

## 3.2 Separable Allocators

A separable allocator generates a matching by decomposing allocation into two successive phases of arbitration. Formally, each phase corresponds to applying an arbitration function  $\Phi$  to each row or column of the request matrix.

For *separable input-first allocation*, as shown in Figure 3.1a, each agent independently selects a single resource to request in the first round. A second round of arbitration is then performed at each resource to select a winner among all incoming requests.

In contrast, for *separable output-first allocation*, shown in Figure 3.1b, agents eagerly forward all of their requests to the associated resources. The latter again

Figure 3.1: Separable allocators with n inputs and m outputs.

Figure 3.2: Example of inefficiency in separable input-first allocation.

perform arbitration among all incoming requests and send grants back to the winning agents. As multiple resources may select the same winning agent in this stage, a second round of arbitration is required in which each agent chooses a winner among all resources that were granted to it in the first stage. Compared to input-first allocation, this incurs additional propagation delay on the timing arc for arbiter state updates as shown in Figure 3.1<sup>2</sup>.

Arbiters—and therefore separable allocators—can be designed such that their delay scales approximately logarithmically with the number of inputs, enabling relatively fast allocation even for high-radix routers. However, because the arbiters in each stage make arbitration decisions independently from one another, multiple arbiters in the first stage can select requests for the same second-stage arbiter from their respective set of available requests, resulting in a non-maximal matching. Figure 3.2 shows an example for separable input-first allocation: Agent 0 and agent 2 both independently select resource 1 in the first arbitration stage, leading to a conflict in the second arbitration stage. Resource 1 can only satisfy one of the two requests, leaving agent 2 unassigned even though it could have used resource 3.

We can reduce the likelihood of such allocation in efficiencies—and consequently increase matching quality—by staggering arbiter priorities using the iSLIP approach

<sup>&</sup>lt;sup>2</sup> The timing paths for  $\tau_{update}$  shown in Figure 3.1a and Figure 3.1b assume that updates are performed according to the *iSLIP* scheme described later in this section.

described in [54]; to this end, we only update the priority state for any given arbiter in the first stage if it produced a request that subsequently resulted in a grant in the second arbitration stage. Further improvements in matching quality can be achieved by performing multiple iterations of separable allocation; however, tight delay constraints typically make this iterative approach unattractive in the context of Networks-on-Chip (NoCs).

## 3.3 Wavefront Allocators

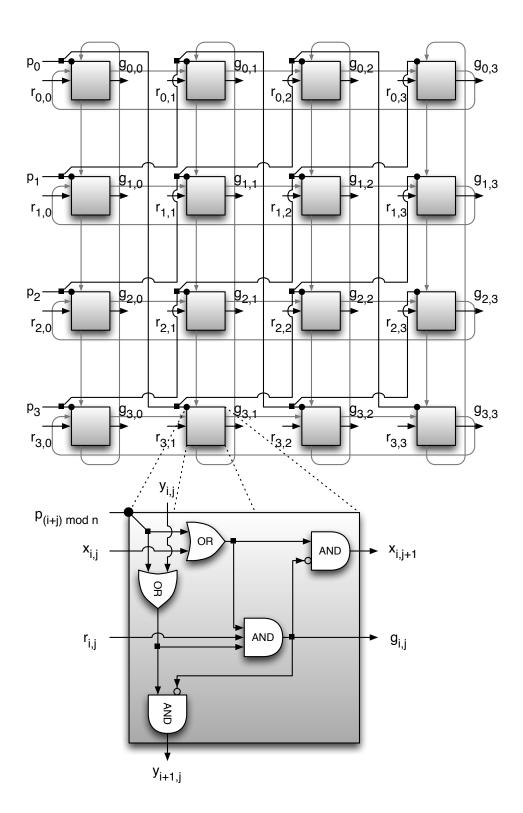

Wavefront allocators [89] take advantage of the fact that, by construction, no two entries on any given diagonal in the request matrix<sup>3</sup> share the same row or column; consequently, all requests on a diagonal can be granted independently of one another. This allows us to compute a maximal matching by first granting all requests on a highest-priority diagonal, eliminating any additional requests in the same rows or columns as the granted requests, and then repeating this process for all remaining diagonals in the request matrix.

Assuming that the diagonals are traversed in linear order, a wavefront allocator can be implemented as a regular array of simple bit cells as shown in Figure 3.3. This facilitates efficient full-custom implementation [21] with area and delay that scales quadratically and approximately linearly with the number of ports, respectively.

Because each row and column of the wavefront array must contain one element of the selected priority diagonal, wavefront allocators are inherently square. If the number of agents and resources differs, a wavefront allocator of sufficient size to accommodate the larger of the two must be used, with the request inputs for any unused bit cells tied to zero.

#### 3.3.1 Fairness

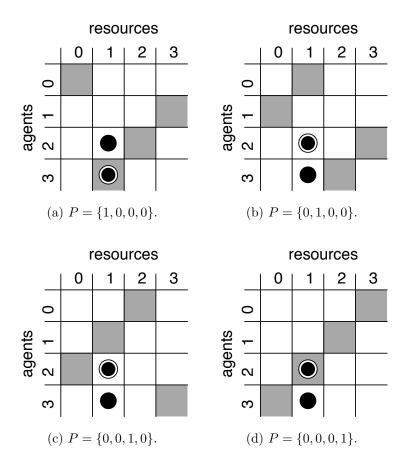

Fairness in wavefront allocators can be controlled by managing the order in which the highest-priority diagonal is selected at the beginning of each round of allocation.

<sup>&</sup>lt;sup>3</sup> Each diagonal corresponds to the set of requests  $r_{i,j}$  for which (i+j) mod n has the same value; i.e., diagonals wrap around at the edges of the matrix.

Figure 3.3: Implementation of a wavefront allocator with n=4 ports.

Figure 3.4: Circular priority diagonal selection results in uneven distribution of grants.

Existing designs commonly implement weak fairness by connecting the priority select signals  $P = \{p_0, p_1, \dots, p_{n-1}\}$  to a circular shift register in which a single bit is set. This approach ensures that any given request will be granted after at most n cycles; however, it can lead to unfair allocation of resources, as the example in Figure 3.4 shows: Because diagonals are evaluated in ascending order, three out of four possible choices for the starting diagonal—indicated by shaded cells—lead to request  $r_{2,1}$  being granted, while request  $r_{3,1}$  is only granted in the one remaining case where the diagonal it is on has highest priority. Thus, on average,  $r_{2,1}$  is granted three times as often as  $r_{3,1}$ .

To facilitate more balanced allocation of resources, we modify the canonical design such that the starting diagonal for the next cycle is selected based on the grants that were generated in the current cycle. Specifically, we extend the priority update mechanism for round-robin arbiters described in Section 2.3 from grant vectors to grant matrices: Whenever one or more grants are produced, the successor of the highest-priority diagonal that had any requests—and, by extension, grants—in the current cycle becomes the starting diagonal in the next cycle. While this is not sufficient to guarantee strong fairness—in particular, if there are requests from all inputs or for all outputs, the behavior is the same as in the canonical implementation—, it avoids pathological behavior when a small number of agents compete for the same resource.

The proposed scheme is readily implemented in hardware by performing an OR reduction across the diagonals of the request matrix, feeding the resulting vector into a round-robin arbiter and connecting the latter's state variable to the wavefront array's priority select inputs  $p_k$ . As the starting diagonal for the next cycle depends only on the request matrix and the starting diagonal for the current cycle, the update can be performed in parallel with the actual allocation and consequently does not extend the allocator's critical path.

## 3.3.2 Acyclic Implementations

As in the case of round-robin arbiters, combinational loops—formed by signals  $x_{i,j}$  and  $y_{i,j}$  in Figure 3.3—can interfere with the ability of commercially available tools

to properly perform static timing analysis. In order to facilitate the use of wavefront allocation with synthesis-based design flows, we develop acyclic alternatives to the canonical design described in [89].

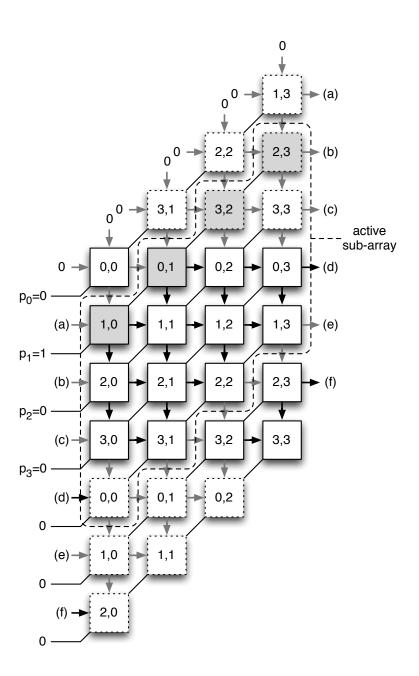

We can eliminate combinational loops by unrolling the wavefront array as we did for linear round-robin arbiters in Section 2.3. Figure 3.5 shows the arrangement of the replicated cells; their grant outputs are ORed with those of the corresponding original cells. The one-hot priority signals  $p_k$  logically divide the extended array into multiple sub-arrays:

- Any part of the extended array above the first active priority diagonal is effectively disabled as the  $x_{i,j}$  and  $y_{i,j}$  signals for each cell (cf. Figure 3.3) are deasserted.

- The first activated priority diagonal marks the beginning of the sub-array in which grants are generated. This sub-array is equivalent to the canonical wave-front array for the current value of the priority signals  $\{p_k\}$  and extends for a total of n successive diagonals.

- Any remaining diagonals at the bottom of the extended array, starting with the second instance of the selected priority diagonal, are also effectively inactive:

Because they replicate earlier active diagonals, any requests in this region of the array are guaranteed to be masked by prior grants.

Hurt et al. [43] describe a similar implementation that uses a sliding window of enable signals to activate a subset of the unrolled array explicitly. All in all, unrolling the wavefront array roughly doubles area, power and critical path delay compared to the canonical implementation.

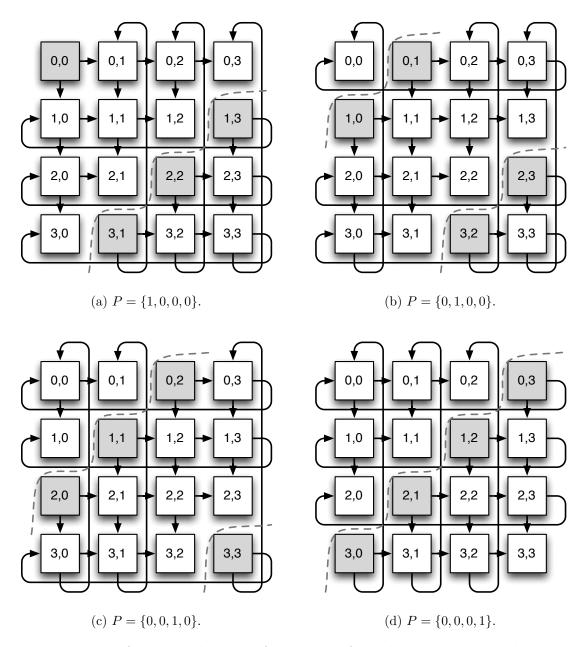

An alternative approach for eliminating the combinational loops takes advantage of the fact that each each of them is logically severed at the currently selected priority diagonal: In the basic cell shown in Figure 3.3, if  $p_{(i+j) \mod n}$  is asserted, the two OR gates mask the values of  $x_i$  and  $y_i$ . Hence, for each individual priority selection, we can construct an equivalent loop-free wavefront array as shown in Figure 3.6. We can use these fixed-priority equivalents to implement an acyclic wavefront allocator.

Figure 3.5: Acyclic wavefront allocator using unrolling with n=4 ports.

Figure 3.6: Loop-free equivalent wavefront arrays for individual priority selections.

Figure 3.7: Acyclic wavefront allocator using input/output transformation.

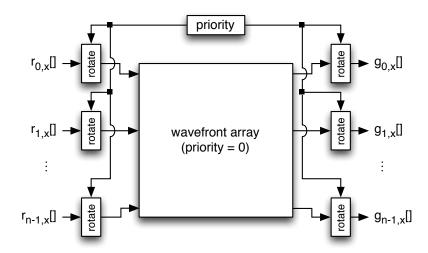

The symmetry of the wavefront array implies that the equivalent array for a given priority k can be derived from that for priority 0 by rotating either each row or each column of the request matrix by k bit positions. Thus, we can construct an acyclic wavefront allocator using a fixed-priority wavefront array and a set of barrel shifters at the inputs and outputs as shown in Figure 3.7. This eliminates the combinational loops at the cost of increased delay.

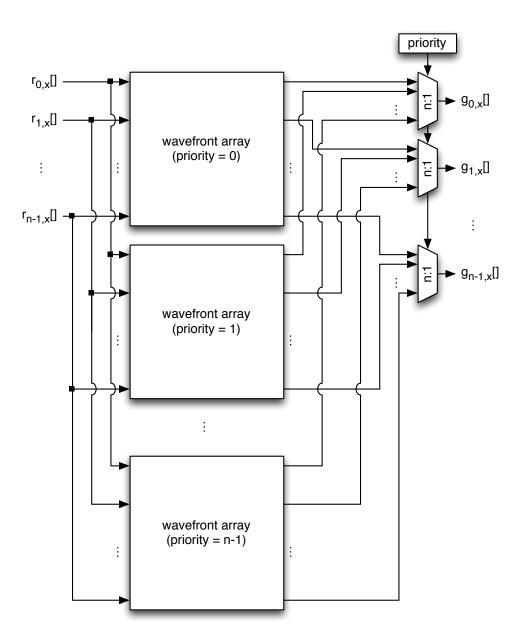

Alternatively, an acyclic implementation can be constructed by applying Shannon decomposition based on the priority selection signals  $p_k$  to the canonical implementation. In this case, the loop-free implementation—as shown in Figure 3.8—computes the resulting grant matrix for each possible priority level in parallel using a set of fixed-priority wavefront arrays; a set of multiplexers then selects the correct intermediate result based on the actual priority value. The replication of wavefront arrays results in cubic scaling behavior for area and power, rendering this approach unattractive for large allocators; however, for allocators with a relatively small number of ports, its comparatively low delay can outweigh the cost differential compared to other implementation alternatives.

Figure 3.8: Acyclic wavefront allocator using replication.

Figure 3.9: Example of starvation in maximum-size allocation.

## 3.4 Maximum-Size Allocation

Conceptually, a maximum matching for a given set of requests and resources is readily found by performing successive iterations of an augmenting path algorithm [26]. However, while hardware implementations have been proposed that can perform one such augmentation step in each cycle [38], the associated complexity as well as the inherently iterative nature of generating a complete matching in this fashion limit their applicability to NoC routers.

Furthermore, given a request matrix, a maximum-size allocator will never generate a grant that is not part of any maximum matching; as a result, it fails to satisfy the elementary fairness property that every request eventually be granted. Figure 3.9 shows an example of a request matrix with two possible maximal matchings that differ in cardinality. In this scenario, a maximum-size allocator will always produce the higher-cardinality matching shown in Figure 3.9b, causing the remaining request to block indefinitely.

However, despite its implementation complexity and susceptibility to starvation, maximum-size allocation provides a useful upper bound on matching quality that other allocators can be benchmarked against.

## 3.5 Evaluation

For separable allocators, implementation trade-offs are largely determined by the characteristics of their constituent arbiters, which we evaluated in Chapter 2. In the present section, we compare the delay, area and energy efficiency of different wavefront allocator implementations. Specifically, we consider the following designs:

Unroll: An acyclic wavefront allocator using unrolling as shown in Figure 3.5.

Rotate: An implementation using input/output transformation (cf. Figure 3.7).

**Replicate:** An implementation using replicated wavefront arrays (cf. Figure 3.8).

**DPA:** A Diagonal Propagation Arbiter<sup>4</sup> as described in [43].

#### 3.5.1 Experimental Setup

We conduct our evaluation using the same experimental setup that was used to compare arbiter implementations in Section 2.7. However, due to the greater logic complexity of wavefront allocators compared to individual arbiters, we begin each sweep at a lower base frequency of 500 MHz.

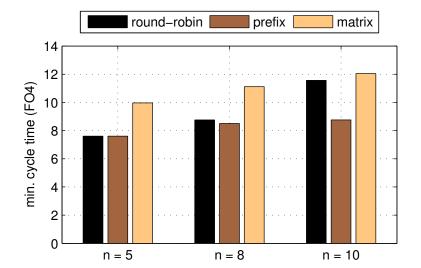

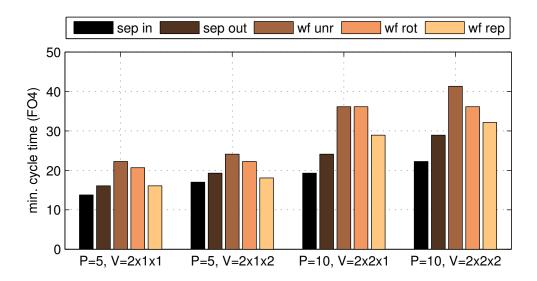

## 3.5.2 Delay

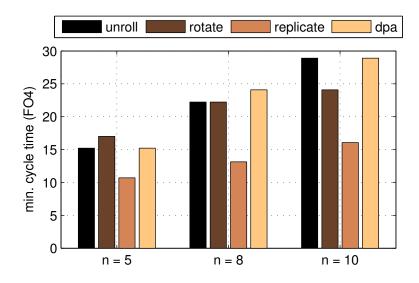

Figure 3.10 compares the minimum cycle time that each implementation alternative can operate at for three exemplary allocator sizes. Due to the expansion of the wavefront block, cycle time grows more quickly for the Diagonal Propagation Arbiter (DPA) and the unrolled implementation as the number of ports increases than for the two other implementations. With n=5 ports, the additional overhead for transforming inputs and outputs increases the delay for the rotation-based allocator by 11% compared to these two implementations; however, its more benign scaling behavior allows it to operate at lower cycle times for configurations with eight or more ports. Despite the overhead associated with creating multiple instances of the

<sup>&</sup>lt;sup>4</sup> Note that, contrary to its name, the DPA is actually an allocator, not an arbiter.

Figure 3.10: Minimum cycle time for n-port wavefront allocators.

central wavefront array, the replication-based implementation is the fastest across all three design points, outperforming the closest competitor in each case by 30–41 %.

#### 3.5.3 Area

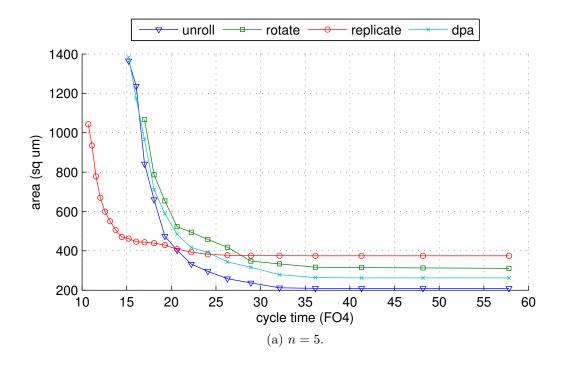

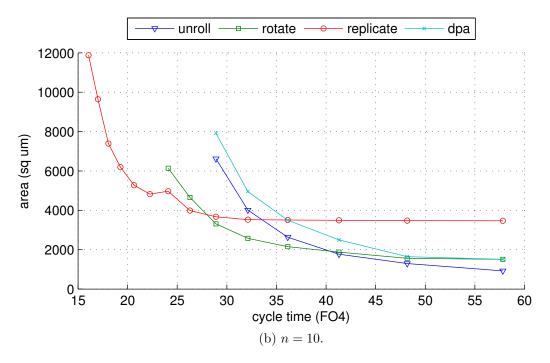

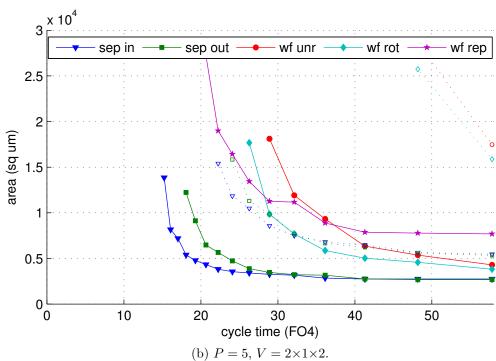

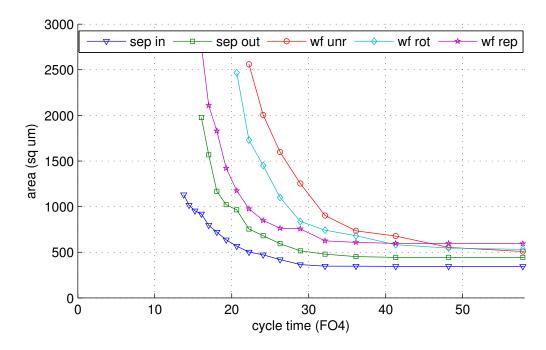

Figure 3.11 shows the area-delay trade-off for the individual wavefront allocator variants; as in Chapter 2, we omit the results for the intermediate configuration (n = 8) for brevity.

With five ports, the unrolled design illustrated in Figure 3.5 yields the best area efficiency among all four designs for cycle times above 20 FO4. While the cost inherent in instantiating multiple wavefront arrays causes the replication-based approach to be less area-efficient for cycle times in excess of 28 FO4, the situation is reversed at the opposite end of the delay spectrum as the higher delay of the other implementation variants necessitates the use of increasingly larger gate sizes in order to meet timing constraints.

For the ten-port configuration, the cubic scaling behavior of the replication-based implementation substantially increases its base cost at low target frequencies. The

Figure 3.11: Area-delay trade-off curves for n-port wavefront allocators.

unrolled implementation continues to require the least area at low operating frequencies; however, due to its lower minimum delay, the rotation-based implementation represents the most area-efficient choice for target cycle times between 28 FO4 and 40 FO4. As in the five-port case, the replication-based implementation achieves the lowest delay overall and thus represents the best trade-off at high target frequencies.

For either design point, at any given target cycle time, at least one of the wavefront implementations described in Section 3.3 provides better area efficiency than the previously proposed implementation from [43].

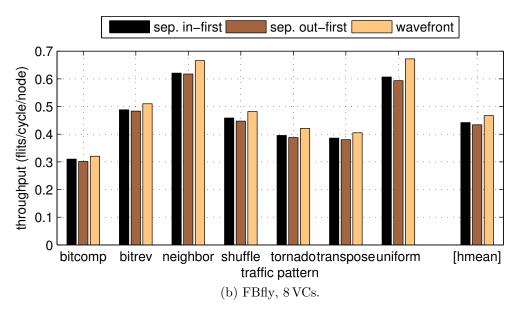

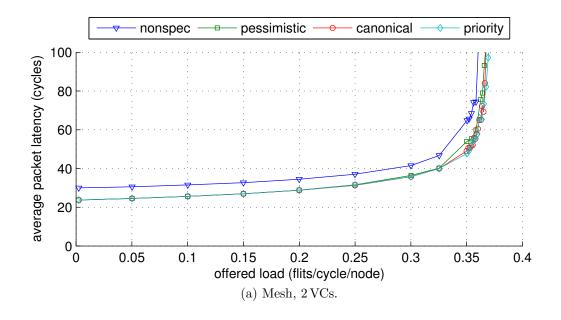

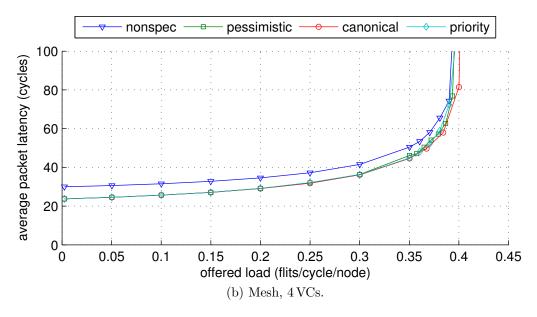

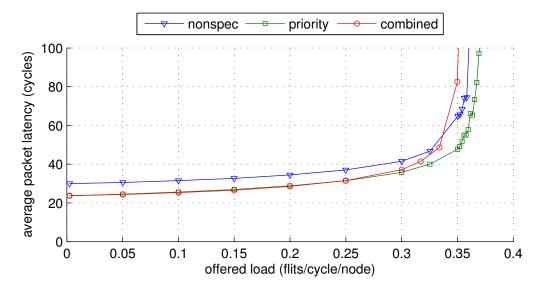

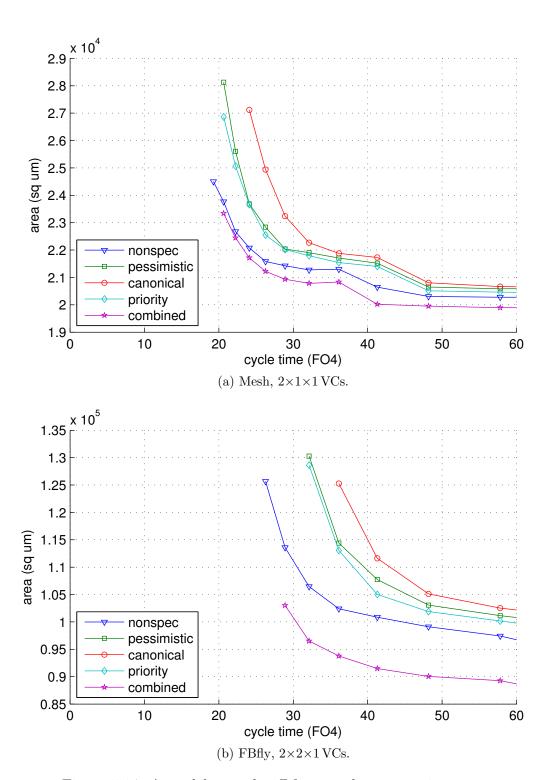

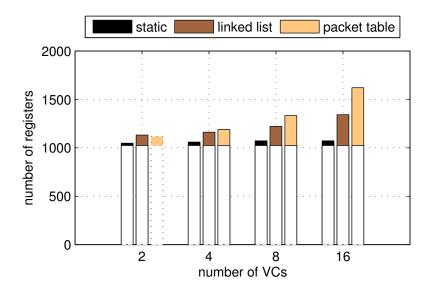

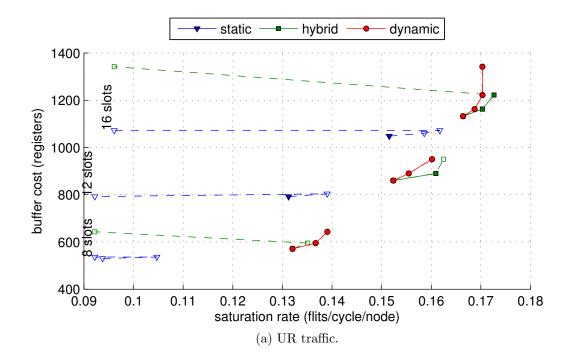

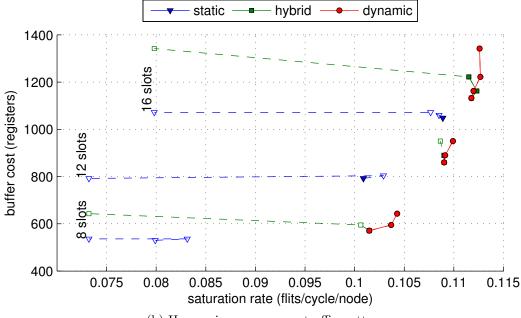

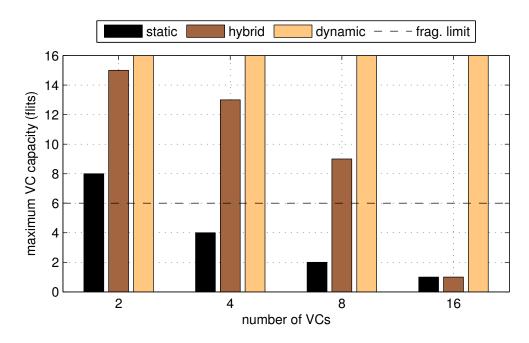

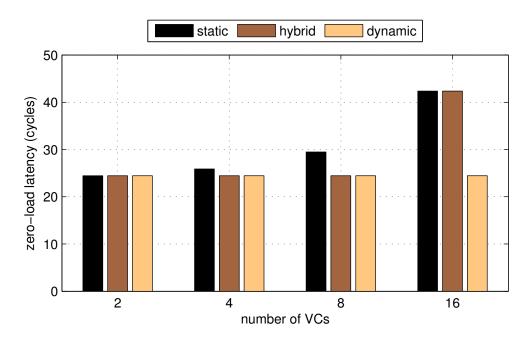

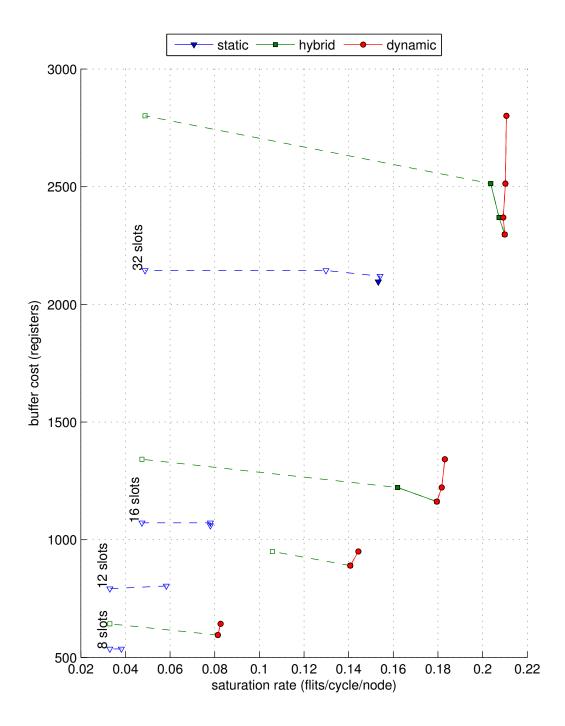

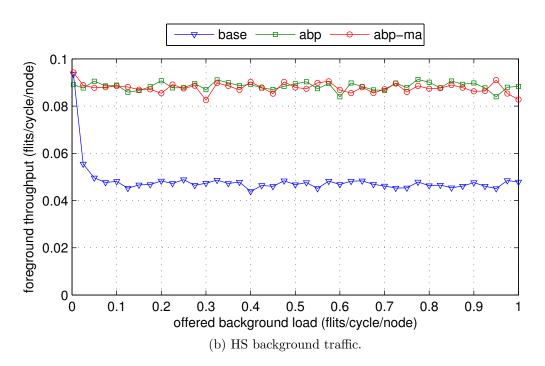

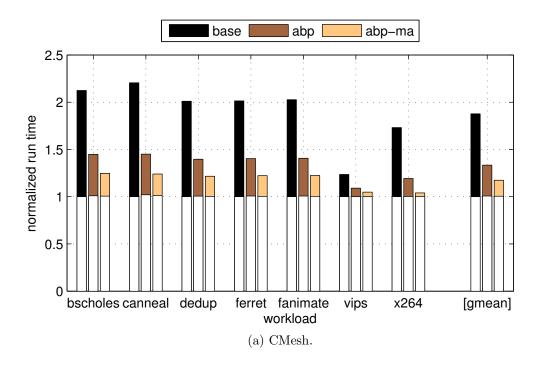

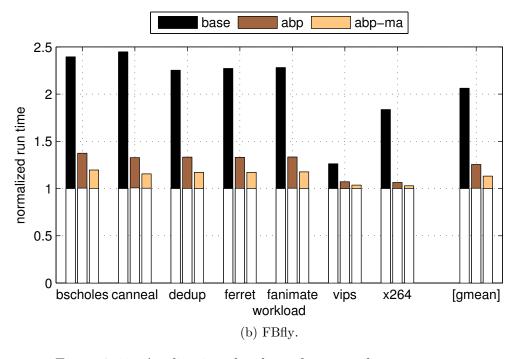

#### 3.5.4 Power-Delay Product