- Research Statement

- Thesis Work: High Speed Serial Links

- Ultrawideband Chaotic Transceiver

- Low-Power Area Efficient Serial Links

- Analog Front-Ends for XDSL

- Electrically Addressable, Liquid Release Well Array

Thesis Work: High Speed Serial Links

Moore's law allows every new generation of CMOS performance to increase at an exponential rate, allowing more computation to occur within that chip. However, a problem occurs when trying to move that information off of that chip and onto another chip, through a "link" whose characteristics don't improve with Moore's law. Thus, chip-to-chip interconnection is one of the leading bottlenecks in computer system performance. Higher and higher data rates for chip-to-chip communication are required to mitigate this growing disparity between on-chip and off-chip bandwidth.

Conventional serial links currently are not scalable towards higher data rates, as the techinques used for timing/clocking are not sufficient at these higher speeds. My thesis work in this area involves addressing this timing uncertainty with a new architecture--essentially incorporating the clock load capacitance directly in to the phase locked loop, eliminating clock buffers. This results in a number of advantages: immunity to power supply noise, higher frequency of operation, low static phase offset, and lower power.

|

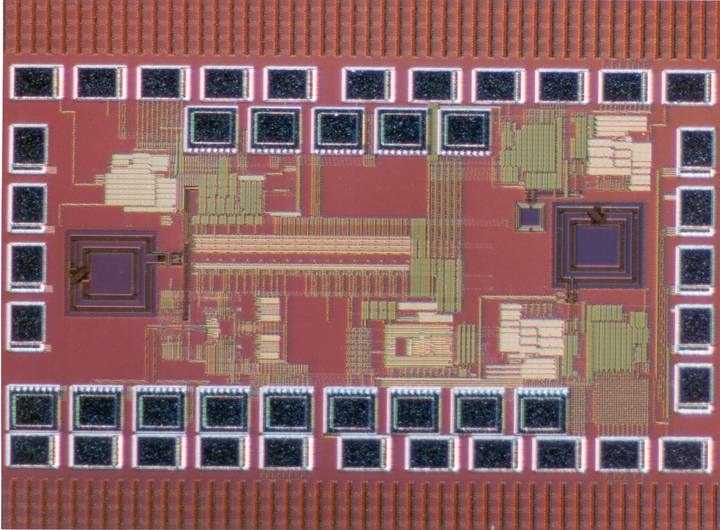

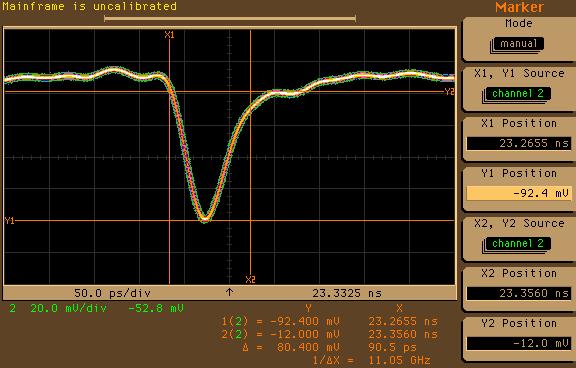

My first test chip, in 0.13um CMOS, is a 20Gb/s CMOS transmitter--achieving one of the fastest data rates

reported, with 4x lower power/area compared to other conventional architectures, allowing for future integration of a large

number of these serial links onto a single die.

Patrick Chiang, William J. Dally, Ming-Ju Edward Lee, Ramesh Senthinathan, Yangjin Oh, and Mark Horowitz. A 20Gb/s 0.13um CMOS Serial Link Transmitter Using an LC-PLL to Directly Drive the Output Multiplexer. IEEE Journal of Solid-State Circuits, Vol. 40, No. 4, April 2005, pp. 1004-1011. |

|

Patrick Chiang, William J. Dally, Ming-Ju Edward Lee, Ramesh Senthinathan, Yangjin Oh, and Mark Horowitz. A 20Gb/s 0.13um CMOS Serial Link Transmitter Using an LC-PLL to Directly Drive the Output Multiplexer. IEEE Symposium on VLSI Circuits, June 15-19, 2004, pp. 272-275. |

|

Patrick Chiang, William J. Dally, Ming-Ju E. Lee. A 20Gb/s 0.13um CMOS Serial Link, IEEE Hotchips 2002, Stanford, CA, Aug. 18-20, 2002. |

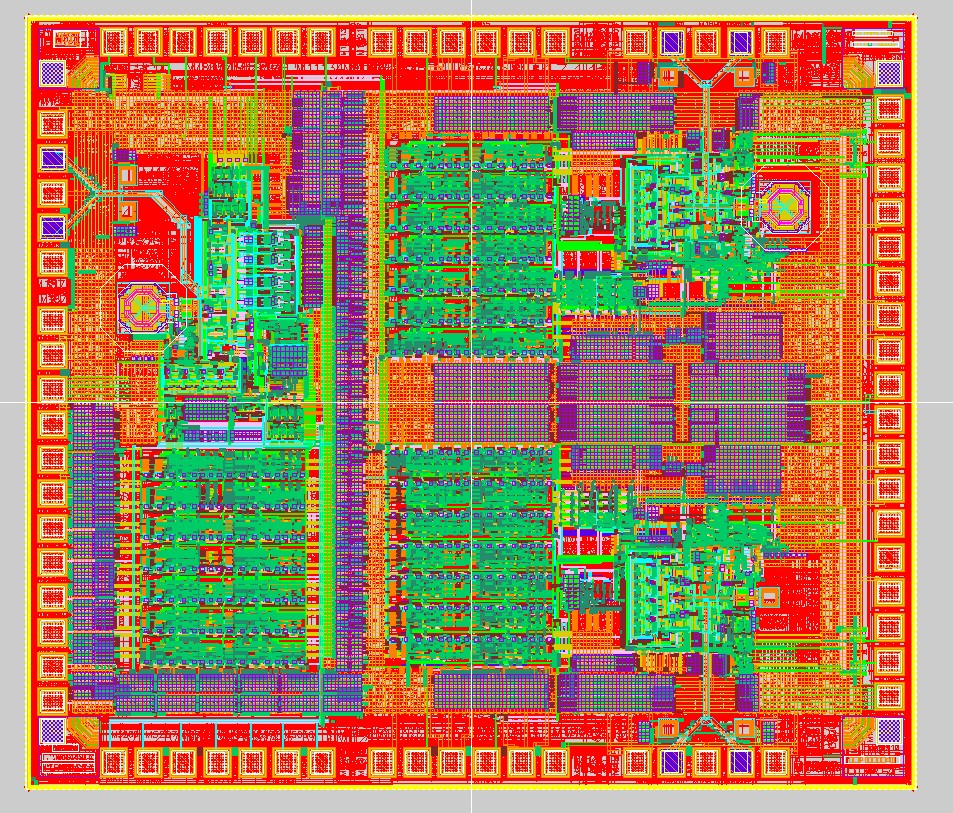

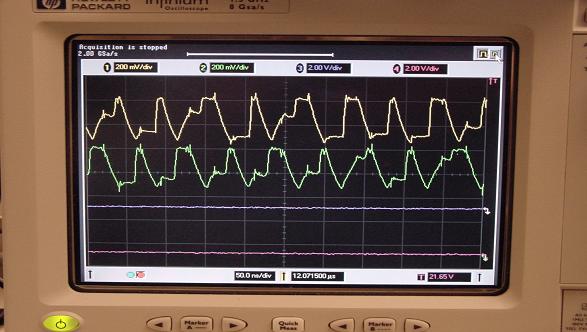

| My second test chip, in 0.13um CMOS using ST Microelectronics, is a completely integrated 20Gb/s transceiver, with a 2nd generation transmitter and a demuxing 20Gb/s receiver. Performance results will be obtained in November 2005. |  |

A 20Mb/s Ultra-Wideband Transceiver in 0.25um CMOS Using Chaotic Pulse Position Modulation

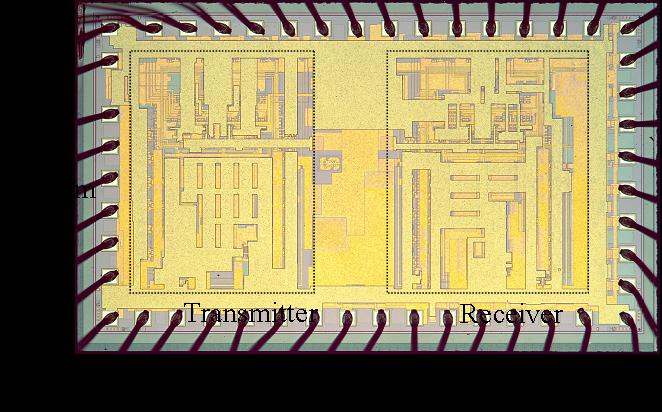

| Through a MURI(Multi-University Research Initiative) with UCSD and UCLA, we built one of the first and only monolithic implementations of a chaotic communications system on a single CMOS die. Designed in a 0.25um CMOS National process, the chip achieves 20Mb/s data rate, dissipating 375mW and BER < 10e-9. A nonlinear chaotic map in the transmitter acts as a spreading carrier for the modulated data, and a similar chaotic map in the receiver recovers the data. |  |

|

Patrick Chiang, William J. Dally, Ming-Ju E. Lee. Monolithic Chaotic Communications System. 2001 IEEE International Conference on Circuits and Systems, Sydney, Australia, May 6-9, 2001.

|

|

CMOS Ultrawideband Techniques

| Ultrawideband RF communication is a relatively new area of research, where the information spans an extremely large frequency range(> 5 GHz) with very low power(< -60dBm), as opposed to traditional narrowband systems, where the bandwidth is very narrow(< 50MHz) with very large power.(~0-10dBm). In the time domain, this can be observed as data encoded in modulated narrow impulses(< 500ps) as opposed to conventional frequency modulation of a continuous signal. Background

The challenge, however, is in creating these extremely short impulses in the time domain. Generally, most people suggest CMOS will be unable to achieve the performance necessary. For example, the MB-OFDM alliance uses an essentially narrowband approach to mimick an ultrawideband impulse in the time domain. For example, using three narrowband carriers and time multiplexing the carriers. Intel's MB-OFDM One possible interesting solution is to use advanced CMOS processes to achieve true impulse radio, using Moore's law scaling to help modulate the transmitter/receivers. For example, using a 20Gb/s transmitter/receiver as designed in my thesis to achieve short aperture impulse radio, one can create a narrow impulse < 80ps wide. In such a manner, true ultrawideband impulse radio in standard CMOS can be made possible, as opposed to conventional techinques such as MB-OFDM, thereby reducing power, area, and complexity. |

|

Low-Power Area Efficient Serial Links

I helped Dr. Ed Lee with his thesis test chips: a low power, low area, 90mW, 4Gb/s Equalized I/O Serial Link

in 0.25um CMOS. These chips demonstrated the concepts of input multiplexed transmitters, supply regulated delay lines,

and offset-compensated slicer/samplers.

Ming-Ju E. Lee, William J. Dally, John W. Poulton, Patrick Chiang, Stephen F. Greenwood. An 84-mW 4Gb/s Clock and Data Recovery Circuit for Serial Link Applications. IEEE Symposium on VLSI Circuits, Kyoto, Japan, June 2001, pp. 149-152.Ming-Ju E. Lee, William Dally, Patrick Chiang. Low-Power Area-Efficient High-Speed I/O Circuit Techniques. IEEE Journal of Solid-State Circuits, November 2000, Vol. 35, No. 11, pp. 1591-1599. Ming-Ju E. Lee, William Dally, Patrick Chiang. A 90mW 4Gb/s Equalized I/O Circuit with Input Offset Cancellation. International Solid State Circuits Conference, San Francisco, February 2000, TP 15.3, pp. 252-253.

|

|

Analog Front-Ends for XDSL

I worked as a design engineer at mixed-signal startup Datapath Systems in 1998, which was subsequently acquired in 2001 by LSI Logic.I designed an automated one-hundred cell low power standard cell library in 0.5um CMOS, the digital backend of a pipelined ADC, and a low power tone detector using a switch capacitor filter.

Cormac Conroy, Samuel Sheng, Arnold Feldman, Greg Uehara, Albert Yeung, Chih-Jen Hung, Vivek Subramanian, Patrick Chiang, Paul Lai, Xiaomin Si, Jerry Fan, David Flynn, Meiqing He. A CMOS Analog Front-End IC for DMT ADSL. International Solid State Circuits Conference, San Francisco, February 1999, pp. 240-241. |

|

An Electrically Addressable, Liquid Release Well Array

| Agilent Technologies and the Department of Mechanical Engineering sponsored a project to create an electrically addressable well array. This microfabricated device uses MEMS processing to create individualized wells to store any releasable liquid--some possible future applications are in drug delivery and reagent microtitration. We built such an array using local resistive heating to thermally heat a thin membrane of SU-8, thereby leading towards a bursted membrane such that the fluid can be released. We built several of these arrays, and proved proof of concept of such a system. | |