Research Contributions

The Imagine Stream Architecture is a novel architecture that executes stream-based programs. It provides high performance with 48 floating-point arithmetic units and a area- and power-efficient register organization. A streaming memory system loads and stores streams from memory. A stream register file provides a large amount of on-chip intermediate storage for streams. Eight VLIW arithmetic clusters perform SIMD operations on streams during kernel execution. Kernel execution is sequenced by a micro-controller. A network interface is used to support multi-Imagine systems and I/O transfers. Finally, a stream controller manages the operation of all of these units.

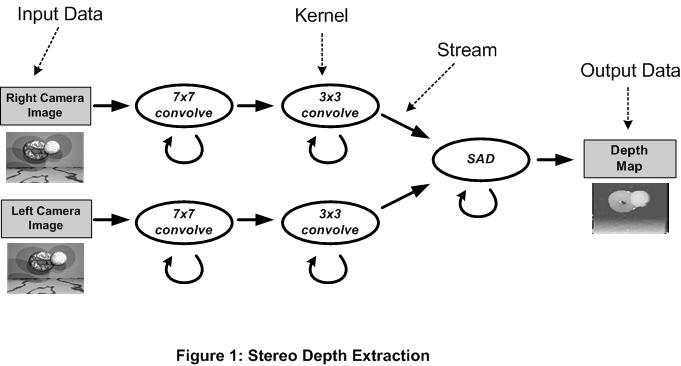

Applications for Imagine are programmed using the stream programming model. This model consists of streams and kernels. Streams are sequences of similar data records. Kernels are small programs which operate on a set of input streams and produce a set of output streams.

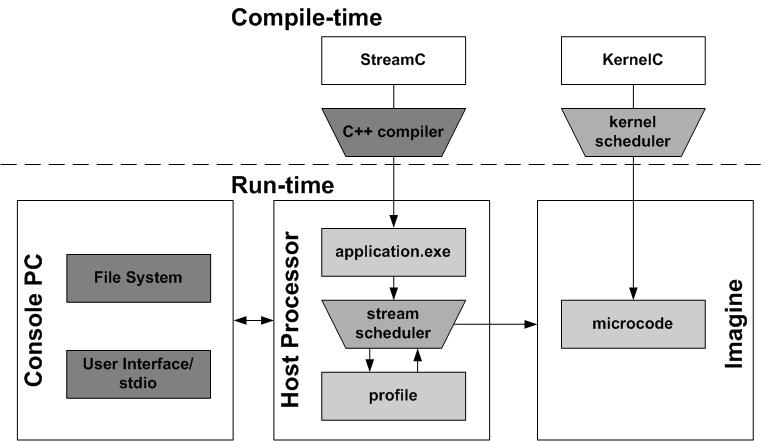

Imagine is programmed with a set of languages and software tools that implement the stream programming model. Applications are programmed in StreamC and KernelC. A stream scheduler maps StreamC to stream instructions for Imagine and a kernel scheduler maps KernelC to VLIW kernel instructions for Imagine. Imagine applications have been tested using a cycle accurate simulator, named ISim, and are currently being tested on a prototype board.

Programmable Graphics and Real-time Media Applications

The Imagine stream processor combines full programmability with high performance. This has enabled research into new real-time media applications such as programmable graphics pipelines.

A prototype Imagine processor was design and fabricated in conjunction with Texas Instruments.and received by Stanford on April 9, 2002. Imagine contains 21 million transistors and has a die size of 16mm x 16mm in a 0.15 micron standard cell technology.

Stream Processor Development Platform

A prototype development board was designed and fabricated in conjunction with ISI-East Dynamic Systems Division. This board has enabled experimental measurements of the prototype Imagine processor, experiments on performance of multi-Imagine systems, and additional application and software tool development.